Введение в дизайн харвера микросхем для тех программистов, которые этим никогда не занимались

Господа! Я периодически встречаю программистов (в том числе хороших), которые имеют совершенно фантастические представления о дизайне хардвера. Например, есть люди, которые думают, что языки описания хадвера Verilog и VHDL транслируются в микрокод, есть люди, которые думают, что микросхемы сейчас дизайнятся с помощью рисования мышкой по экрану, и есть люди, которые не знают, зачем в микросхемах clock, то бишь синхросигнал.

Поэтому я написал текст под катом, чтобы на уровне примерно 5-го класса средней щколы сделать введение в данные материи. Зачем это нужно? Я думаю, что то, что я написал, может быть интересным следующим трем группам:

1. Юным программистам, которые могут захотеть внести коррекцию в свои планы карьеры, и выучиться не на гуру операционных систем или компиляторов, а на дизайнеров микропроцессоров и графических чипов используя методологию RTL (register-transfer-level - уровень регистровых передач, не путать с другими расшифровками этой аббревиатуры).

2. Алгоритмически-ориентированным программистам среднего возраста, которые могут захотеть сделать карьеру в логически сложных средствах проектирования электроники (Electronic Design Automation). Я сам работал в индустрии средств проектирования электроники больше 15 лет, после чего перешел в саму электронную индустрию.

3. Опытным программистам, которые могут захотеть сменить карьеру с например писания ООП приложений на Джаве на карьеру в Design Verification на SystemVerilog - это создание фреймворков, которые тестируют хардверные дизайны на прочность, бомбардируя их превдослучайными транзакциями и учитывая functional coverage (это сейчас модно и хорошо оплачивается).

Итого. В последние 20 лет дизайн чаще всего пишется на языке Verilog (в Европе и у военных - VHDL), после чего специальная программа (logic synthesis) превращает дизайн в граф из проводов и логических примитивов, другая программа (static timing analysis) сообщает дизайнеру, вписывается ли он в бюджет скорости, а третья программа (place-and-route) раскладывает этот дизайн по площадке микросхемы.

Когда дизайн проходит все этапы: кодирование на верилоге, отладка, верификация, синтез, static timing analysis, floorplanning, place-n-route, parasitics extraction и т.д. - получается файл под названием GDSII, который отправляют на фабрику, и фабрика выпекает микросхемы. Самые известные фабрики этого типа принадлежат компании Taiwan Semiconductor Manufacturing Company или TSMC.

Теперь допустим, нам нужно сделать микросхему - счетчик, которая бы выводила в цикле числа 0, 1, 2, 3, 0, 1, 2, 3, ...

Пишем на SystemVerilog:

module counter

(

input clock,

input reset,

output logic [1:0] n

);

always @(posedge clock)

begin

if (reset)

n <= 0;

else

n <= n + 1;

end

endmodule

Это означает: Имеется модуль, в который идет два провода - clock (синхросигнал, который идет вверх-вниз-вверх-вниз-...) и reset (сброс в начальное состояние). Из модуля выходит тоже два провода, которые образуют одно двухбитное число, которое на каждом биении синхросигнала увеличивают значение на единицу (по модулю 4). Иными словами: на каждом положительном фронте сигнала (clock edge) смотреть на провод reset. Если reset равен 1, то обнулить внутренний регистр (подсоединенный к выводу), если reset равен 0, то увеличить число, хранящееся в этом регистре на единицу.

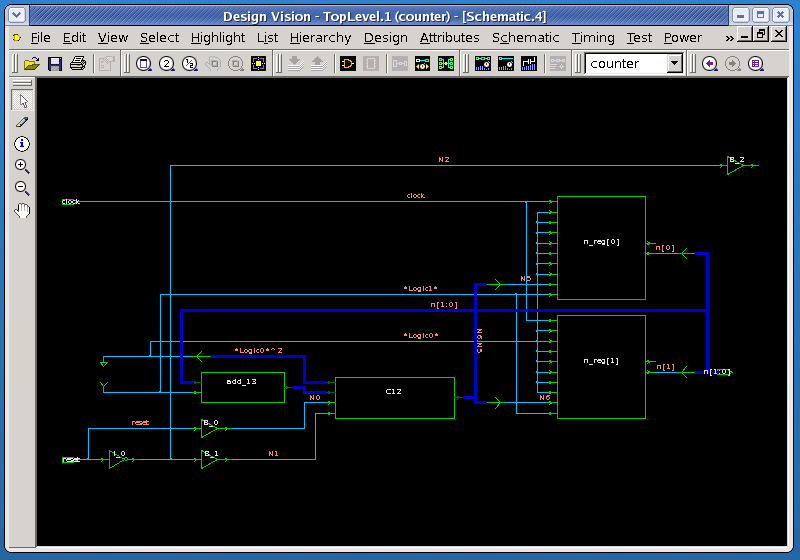

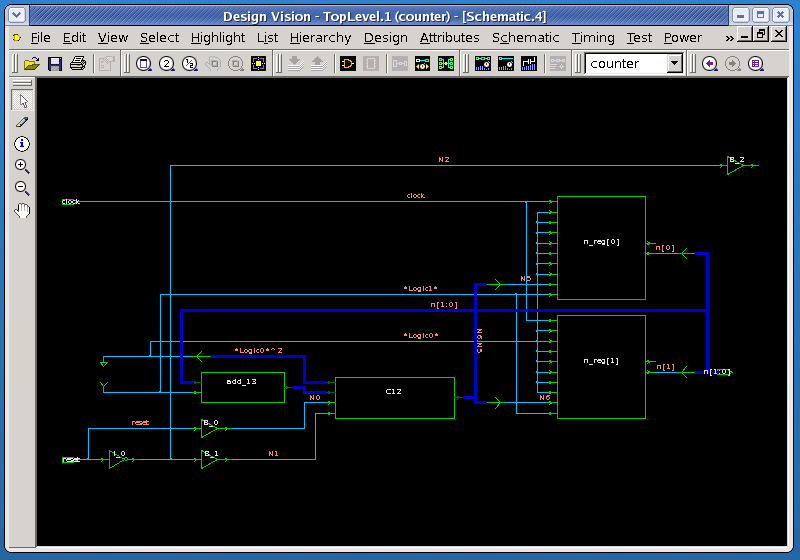

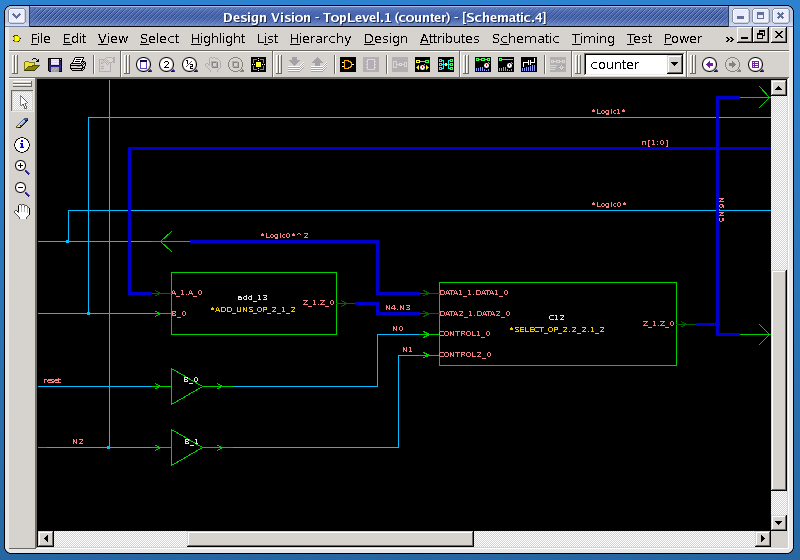

Теперь если скормить этот код синтезис-тулу, в нашем случае Synopsys Design Compiler, то он превратит его вот в такую схему:

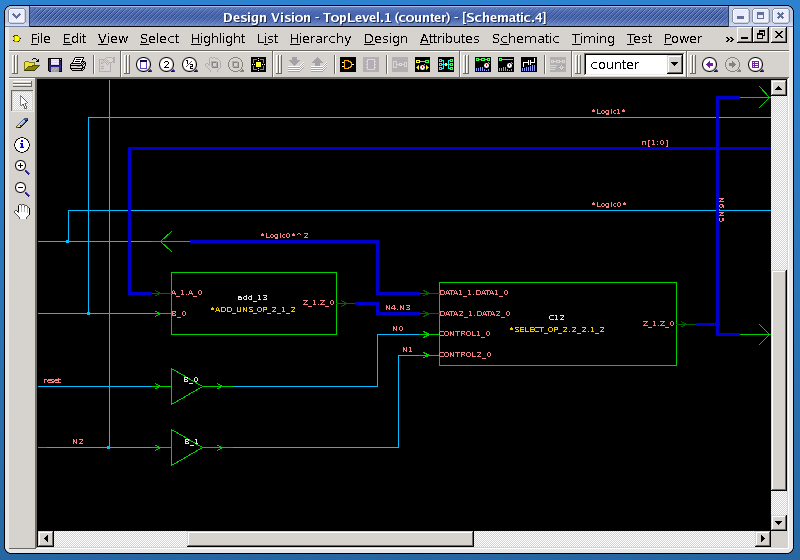

Если покрупнее фрагмент:

Схема выглядит мудрено, но на самом деле она работает так:

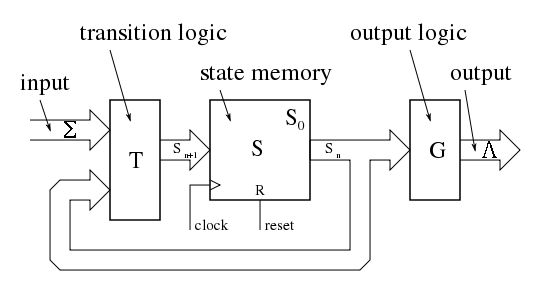

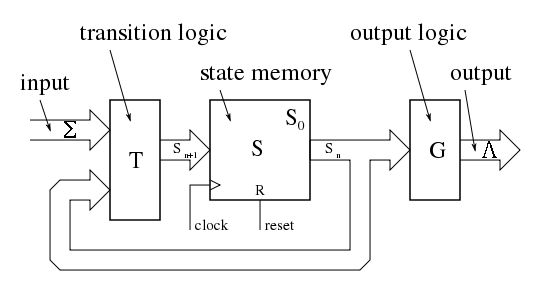

Note: Да, я знаю, что это "проще" реализовать с помощью двух T-flip-flops, но я показал это именно так, чтобы иллюстрировать общий принцип "комбинаторная логика + флип-флопы" (см. картинка с википедии):

Разъяснение что есть что:

Квадратик слева - сумматор, такой комбинаторный дизайн, которые берет на входе два числа и через некоторое время T выдает на выходе их сумму. До истечения времени T на выходе сумматора будут находиться какие-то неопределенные значения, а после T все устаканится.

Время T должно быть меньше, чем время между пульсами синхросигнала. Точнее, наоборот. Дизайнер задаёт программе-синтесайзеру, с какой частотой он хочет гонять дизайн, и программа подбирает подходящий сумматор (быстрый-большой, медленный-маленький и т.д.) под эту частоту. Если получится.

Квадратик справа - это флип-флоп (называемая по-русски "триггер"), такая фиговина, которая хранит бит информации между пульсами синхросигнала. Пока всякая арифметика в сумматоре устаканивается, булькает и чавкает, в это время флип-флоп хранит значение с предыдущего цикла часов/синхросигнала и отдает его только в качестве read-only значения для вычислений.

В конце-концов вся комбинаторная логика (сумматор) устаканивается, и наконец приходит положительный фронт синхросигнала, который разрешает флип-флопу записать новые значения для следующего цикла.

С помощью модулей, гейтов (элементов комбинаторной логики - "и", "или", "нет" и т.д.) и флип-флопов в принципе можно реализовать весь хардвер. И любой алгоритм. Причем с высокой степенью параллельности. Можно хоть сто чисел складывать за наносекунду, если очень хочется и есть достаточно много гейтов и ваттов (хотя про ватты - это более тонкий вопрос).

Теперь как это отлаживать? А очень просто. В язык Verilog входит не только "synthesizable subset" (подмножество языка, код на котором в конечном итоге становится силиконовыми дорожками и силиконовыми транзисторами, переключающимися за наносекунды).

В верилог входит еще и "behavioral level", кучу конструкций для обыкновенного программирования, которые позволяют писать на верилоге высокоуровневые модели и тесты для симуляции блоков, процессоров и систем на обычных компьютерах.

Например, тест для нашего счетчика может выглядеть так:

module testbench;

// Декларируем провода

logic clock;

logic reset;

logic [1:0] n;

// Адын инстанс модуля counter

counter counter_instance (clock, reset, n);

// Инициализируем и врубаем синхросигнал,

// меняющий значение каждые 5 условных наносекунд

initial clock = 0;

always # 5 clock = ~ clock;

// Через два цикла синхросигнала запускаем reset,

// Держим его еще два цикла, запускаем обратно

initial

begin

reset <= 0;

repeat (2) @(posedge clock);

reset <= 1;

repeat (2) @(posedge clock);

reset <= 0;

end

initial

begin

// Записываем все изменения сигналов в файл

$dumpvars (0, counter_instance);

// Печатаем на экране

$display ("time clock reset n");

$monitor (" %2d %b %b %b", $time, clock, reset, n);

repeat (10) @(posedge clock);

$finish;

end

endmodule

Теперь запустим все это дело на симуляторе верилога, например Cadence NC-Verilog:

ncverilog +access+r +sv counter.sv testbench.sv

ncsim> run

time clock reset n

0 0 0 xx

5 1 0 xx

10 0 0 xx

15 1 1 xx

20 0 1 xx

25 1 1 00

30 0 1 00

35 1 0 00

40 0 0 00

45 1 0 01

50 0 0 01

55 1 0 10

60 0 0 10

65 1 0 11

70 0 0 11

75 1 0 00

80 0 0 00

85 1 0 01

90 0 0 01

Simulation complete via $finish(1) at time 95 NS + 0

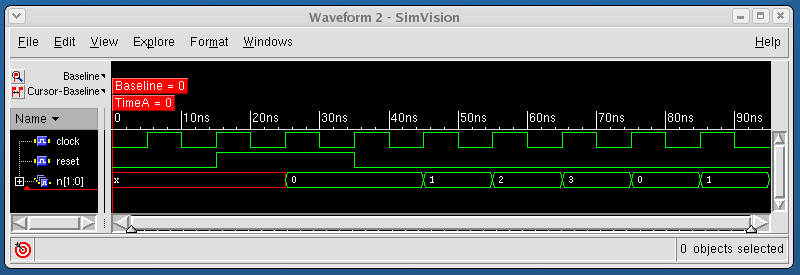

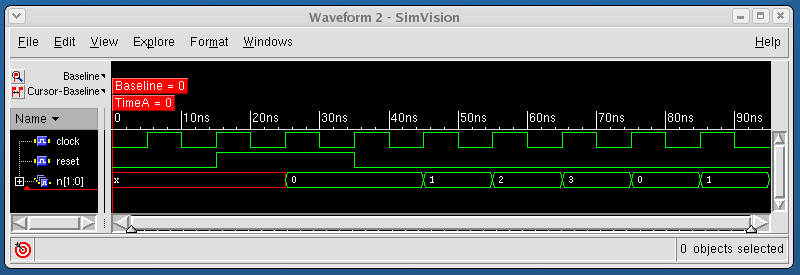

Но харвер-инжинеры и хардвер-верификейшн-инжинеры редко отлаживаются с помощью printf-ов, то бишь $display-statement-ов. Гораздо удобнее смотреть на сигналы с помощью так называемого waveform viewer:

В больших дизайнах больше кода на Верилоге, но суть примерно та же. Вот например на этой картинке изображен один из ранних конвейерных RISC-микропроцессоров архитектуры MIPS с пятью стадиями конвейера (Fetch, Decode, Execute, Memory Access, Write Back). Вы видите пять рядов флип-флопов и пять комбинаторных облаков, соответствующих пяти стадиям конвейера, через который проходят извлеченные из памяти команды процессора:

Дополнение 1. Кусок моей старой неопубликованной статьи про индустрию автоматизации электронного дизайна (Electronic Design Automation или EDA) (поленился окончить и опубликовать в своё время):

Дизайнеры электроники используют специальные программы, для разработки которых возникла индустрия автоматизации электронного дизайна (Electronic Design Automation или EDA). Сама по себе индустрия EDA невелика - ее рынок менее $ 5 млрд долларов, но она «питается» на гораздо более крупной индустрии дизайна и производства микросхем ($200 млрд долл), которая в свою очередь стоит на огромной (более $1 триллиона долл) мировой индустрии электронных систем, которая выпускает всю электронику - от наручных часов до систем управления спутниками. Самая большая часть рынка EDA находится в США, за ним идет Япония, затем Европа и быстрорастущий рынок Китая и других восточноазиатских стран. Многие EDA компании имеют штаб-квартиру в калифорнийской Силиконовой Долине и группы разработчиков в других частях света - в Индии, Китае, Европе, Южной Корее, Тайване или Израиле.

В конце 1950-х годов цифровая электроника строилась на основе транзисторов в отдельных корпусах на трех ножках. Первую микросхему изобрел в 1958 году инженер из компании Texas Instruments Джек Килби (Jack Kilby), который получил за это изобретение нобелевскую премию 2000 года. Но микросхема Килби была на основе полупроводника германия, а первую микросхему на основе кремния изобрел Роберт Нойс (Robert Noyce) из Fairchild Semiconductor, который работал независимо от Килби, но сделал свою микросхему на полгода позже. Первым компьютером, построенным на микросхемах, был Apollo Guidance Computer (1962), который стоял в космических кораблях, приземлившихся на Луну.

Программы, помогающие инженерам проектировать микросхемы, стали возникать еще в 1960-х. Сначала это были графические редакторы, в которых можно было прямоугольниками разных цветов рисовать слои разных типов на поверхности микросхемы. В 1970-х количество транзисторов на одной микросхеме стало исчисляться тысячами и технология изменилась - инженеры стали вводить дизайн как сеть из логических элементов («и», «или», «не», ячеек памяти), после чего специальная программа (place-and-route) автоматически расставляла логические элементы по площадке микросхемы и соединяла их дорожками. В это же время появились программы-симуляторы, позволяющие промоделировать поведение микросхемы до воплощения ее в кремнии.

«Золотым веком» EDA стали 1980 годы, когда EDA выделилась как самостоятельная индустрия (сноска: До 1980-х EDA рассматривалась как часть индустрии CAD (Computer Aided Design) или по-русски САПР (Системы Автоматизированного ПРоектирования) - индустрии, занимавшейся также механическим дизайном). В 1981 году возникла первая тройка индустриальных лидеров - компании Daisy Systems, Mentor Graphics и Valid Logic, которые сокращенно называли DMV (сноска: игра слов - DMV - это также Department of Motor Vehicles, автотранспортная инспекция). Возникли языки дизайна Verilog и VHDL и технология логического синтеза, которые вместе позволяли инженеру писать логические и математические выражения в виде текста, а не рисовать кропотливо сеть из логических элементов с помощью мышки на экране.

В 1990-х количество транзисторов на кристалле стало ограничиваться не возможностями станков на фабрике, а производительностью труда инженеров. После окончания «холодной войны» с СССР, главными клиентами EDA-компаний стали не военные, а производители потребительской электроники.

Дополнение 2 - Список рекомендуемой литературы:

Из учебников для самых начинающих лично мне больше всего понравилась David Harris, Sarah Harris. Digital Design and Computer Architecture.

Там есть и про логику, и про HDL, и введение в процессоры:

С этой книжкой можно просто взять в руки какой-нибудь бесплатный симулятор верилога - и вперед.

Также для самого-самого начала есть полезная книжка для "легкого чтения" с описанием работы дизайнеров для нетехнических людей (например маркетологов):

Essential Electronic Design Automation (EDA)

Mark D. Birnbaum

Есть также стандартная вводная книжка Patterson & Hennesy для студентов начальных курсов, но она ИМХО слишком многословная и разбавленная, кроме этого она более софтверная, чем хардверная, т.е. вначале слишком много ассемблера (для того кто уже знает, будет неинтересно):

David A. Patterson, John L. Hennessy. Computer Organization and Design, Fourth Edition: The Hardware/Software Interface.

Далее есть более продвинутая и тоже стандартная университетская книжка, но ИМХО не очень хорошо структурированная:

Computer Architecture: A Quantitative Approach, 4th Edition

John L. Hennessy, David A. Patterson

Занятная книженция с историческими статьями про изобретения тех или иных микропроцессорных штучек:

Readings in Computer Architecture (The Morgan Kaufmann Series in Computer Architecture and Design)

Mark D. Hill, Norman P. Jouppi, Gurindar S. Sohi

Вот есть еще новая книжка, которую я не читал, но судя по оглавлению,

там есть многие нужные вещи:

Microprocessor Architecture

Jean-Loup Baer

Для многих адванснутых штучек нужно читать университетские статьи. Например про многоядерность и когерентные кэши книг мало, зато статей на интернете самого разного уровня понятности - навалом.

Poll

Поэтому я написал текст под катом, чтобы на уровне примерно 5-го класса средней щколы сделать введение в данные материи. Зачем это нужно? Я думаю, что то, что я написал, может быть интересным следующим трем группам:

1. Юным программистам, которые могут захотеть внести коррекцию в свои планы карьеры, и выучиться не на гуру операционных систем или компиляторов, а на дизайнеров микропроцессоров и графических чипов используя методологию RTL (register-transfer-level - уровень регистровых передач, не путать с другими расшифровками этой аббревиатуры).

2. Алгоритмически-ориентированным программистам среднего возраста, которые могут захотеть сделать карьеру в логически сложных средствах проектирования электроники (Electronic Design Automation). Я сам работал в индустрии средств проектирования электроники больше 15 лет, после чего перешел в саму электронную индустрию.

3. Опытным программистам, которые могут захотеть сменить карьеру с например писания ООП приложений на Джаве на карьеру в Design Verification на SystemVerilog - это создание фреймворков, которые тестируют хардверные дизайны на прочность, бомбардируя их превдослучайными транзакциями и учитывая functional coverage (это сейчас модно и хорошо оплачивается).

Итого. В последние 20 лет дизайн чаще всего пишется на языке Verilog (в Европе и у военных - VHDL), после чего специальная программа (logic synthesis) превращает дизайн в граф из проводов и логических примитивов, другая программа (static timing analysis) сообщает дизайнеру, вписывается ли он в бюджет скорости, а третья программа (place-and-route) раскладывает этот дизайн по площадке микросхемы.

Когда дизайн проходит все этапы: кодирование на верилоге, отладка, верификация, синтез, static timing analysis, floorplanning, place-n-route, parasitics extraction и т.д. - получается файл под названием GDSII, который отправляют на фабрику, и фабрика выпекает микросхемы. Самые известные фабрики этого типа принадлежат компании Taiwan Semiconductor Manufacturing Company или TSMC.

Теперь допустим, нам нужно сделать микросхему - счетчик, которая бы выводила в цикле числа 0, 1, 2, 3, 0, 1, 2, 3, ...

Пишем на SystemVerilog:

module counter

(

input clock,

input reset,

output logic [1:0] n

);

always @(posedge clock)

begin

if (reset)

n <= 0;

else

n <= n + 1;

end

endmodule

Это означает: Имеется модуль, в который идет два провода - clock (синхросигнал, который идет вверх-вниз-вверх-вниз-...) и reset (сброс в начальное состояние). Из модуля выходит тоже два провода, которые образуют одно двухбитное число, которое на каждом биении синхросигнала увеличивают значение на единицу (по модулю 4). Иными словами: на каждом положительном фронте сигнала (clock edge) смотреть на провод reset. Если reset равен 1, то обнулить внутренний регистр (подсоединенный к выводу), если reset равен 0, то увеличить число, хранящееся в этом регистре на единицу.

Теперь если скормить этот код синтезис-тулу, в нашем случае Synopsys Design Compiler, то он превратит его вот в такую схему:

Если покрупнее фрагмент:

Схема выглядит мудрено, но на самом деле она работает так:

Note: Да, я знаю, что это "проще" реализовать с помощью двух T-flip-flops, но я показал это именно так, чтобы иллюстрировать общий принцип "комбинаторная логика + флип-флопы" (см. картинка с википедии):

Разъяснение что есть что:

Квадратик слева - сумматор, такой комбинаторный дизайн, которые берет на входе два числа и через некоторое время T выдает на выходе их сумму. До истечения времени T на выходе сумматора будут находиться какие-то неопределенные значения, а после T все устаканится.

Время T должно быть меньше, чем время между пульсами синхросигнала. Точнее, наоборот. Дизайнер задаёт программе-синтесайзеру, с какой частотой он хочет гонять дизайн, и программа подбирает подходящий сумматор (быстрый-большой, медленный-маленький и т.д.) под эту частоту. Если получится.

Квадратик справа - это флип-флоп (называемая по-русски "триггер"), такая фиговина, которая хранит бит информации между пульсами синхросигнала. Пока всякая арифметика в сумматоре устаканивается, булькает и чавкает, в это время флип-флоп хранит значение с предыдущего цикла часов/синхросигнала и отдает его только в качестве read-only значения для вычислений.

В конце-концов вся комбинаторная логика (сумматор) устаканивается, и наконец приходит положительный фронт синхросигнала, который разрешает флип-флопу записать новые значения для следующего цикла.

С помощью модулей, гейтов (элементов комбинаторной логики - "и", "или", "нет" и т.д.) и флип-флопов в принципе можно реализовать весь хардвер. И любой алгоритм. Причем с высокой степенью параллельности. Можно хоть сто чисел складывать за наносекунду, если очень хочется и есть достаточно много гейтов и ваттов (хотя про ватты - это более тонкий вопрос).

Теперь как это отлаживать? А очень просто. В язык Verilog входит не только "synthesizable subset" (подмножество языка, код на котором в конечном итоге становится силиконовыми дорожками и силиконовыми транзисторами, переключающимися за наносекунды).

В верилог входит еще и "behavioral level", кучу конструкций для обыкновенного программирования, которые позволяют писать на верилоге высокоуровневые модели и тесты для симуляции блоков, процессоров и систем на обычных компьютерах.

Например, тест для нашего счетчика может выглядеть так:

module testbench;

// Декларируем провода

logic clock;

logic reset;

logic [1:0] n;

// Адын инстанс модуля counter

counter counter_instance (clock, reset, n);

// Инициализируем и врубаем синхросигнал,

// меняющий значение каждые 5 условных наносекунд

initial clock = 0;

always # 5 clock = ~ clock;

// Через два цикла синхросигнала запускаем reset,

// Держим его еще два цикла, запускаем обратно

initial

begin

reset <= 0;

repeat (2) @(posedge clock);

reset <= 1;

repeat (2) @(posedge clock);

reset <= 0;

end

initial

begin

// Записываем все изменения сигналов в файл

$dumpvars (0, counter_instance);

// Печатаем на экране

$display ("time clock reset n");

$monitor (" %2d %b %b %b", $time, clock, reset, n);

repeat (10) @(posedge clock);

$finish;

end

endmodule

Теперь запустим все это дело на симуляторе верилога, например Cadence NC-Verilog:

ncverilog +access+r +sv counter.sv testbench.sv

ncsim> run

time clock reset n

0 0 0 xx

5 1 0 xx

10 0 0 xx

15 1 1 xx

20 0 1 xx

25 1 1 00

30 0 1 00

35 1 0 00

40 0 0 00

45 1 0 01

50 0 0 01

55 1 0 10

60 0 0 10

65 1 0 11

70 0 0 11

75 1 0 00

80 0 0 00

85 1 0 01

90 0 0 01

Simulation complete via $finish(1) at time 95 NS + 0

Но харвер-инжинеры и хардвер-верификейшн-инжинеры редко отлаживаются с помощью printf-ов, то бишь $display-statement-ов. Гораздо удобнее смотреть на сигналы с помощью так называемого waveform viewer:

В больших дизайнах больше кода на Верилоге, но суть примерно та же. Вот например на этой картинке изображен один из ранних конвейерных RISC-микропроцессоров архитектуры MIPS с пятью стадиями конвейера (Fetch, Decode, Execute, Memory Access, Write Back). Вы видите пять рядов флип-флопов и пять комбинаторных облаков, соответствующих пяти стадиям конвейера, через который проходят извлеченные из памяти команды процессора:

Дополнение 1. Кусок моей старой неопубликованной статьи про индустрию автоматизации электронного дизайна (Electronic Design Automation или EDA) (поленился окончить и опубликовать в своё время):

Дизайнеры электроники используют специальные программы, для разработки которых возникла индустрия автоматизации электронного дизайна (Electronic Design Automation или EDA). Сама по себе индустрия EDA невелика - ее рынок менее $ 5 млрд долларов, но она «питается» на гораздо более крупной индустрии дизайна и производства микросхем ($200 млрд долл), которая в свою очередь стоит на огромной (более $1 триллиона долл) мировой индустрии электронных систем, которая выпускает всю электронику - от наручных часов до систем управления спутниками. Самая большая часть рынка EDA находится в США, за ним идет Япония, затем Европа и быстрорастущий рынок Китая и других восточноазиатских стран. Многие EDA компании имеют штаб-квартиру в калифорнийской Силиконовой Долине и группы разработчиков в других частях света - в Индии, Китае, Европе, Южной Корее, Тайване или Израиле.

В конце 1950-х годов цифровая электроника строилась на основе транзисторов в отдельных корпусах на трех ножках. Первую микросхему изобрел в 1958 году инженер из компании Texas Instruments Джек Килби (Jack Kilby), который получил за это изобретение нобелевскую премию 2000 года. Но микросхема Килби была на основе полупроводника германия, а первую микросхему на основе кремния изобрел Роберт Нойс (Robert Noyce) из Fairchild Semiconductor, который работал независимо от Килби, но сделал свою микросхему на полгода позже. Первым компьютером, построенным на микросхемах, был Apollo Guidance Computer (1962), который стоял в космических кораблях, приземлившихся на Луну.

Программы, помогающие инженерам проектировать микросхемы, стали возникать еще в 1960-х. Сначала это были графические редакторы, в которых можно было прямоугольниками разных цветов рисовать слои разных типов на поверхности микросхемы. В 1970-х количество транзисторов на одной микросхеме стало исчисляться тысячами и технология изменилась - инженеры стали вводить дизайн как сеть из логических элементов («и», «или», «не», ячеек памяти), после чего специальная программа (place-and-route) автоматически расставляла логические элементы по площадке микросхемы и соединяла их дорожками. В это же время появились программы-симуляторы, позволяющие промоделировать поведение микросхемы до воплощения ее в кремнии.

«Золотым веком» EDA стали 1980 годы, когда EDA выделилась как самостоятельная индустрия (сноска: До 1980-х EDA рассматривалась как часть индустрии CAD (Computer Aided Design) или по-русски САПР (Системы Автоматизированного ПРоектирования) - индустрии, занимавшейся также механическим дизайном). В 1981 году возникла первая тройка индустриальных лидеров - компании Daisy Systems, Mentor Graphics и Valid Logic, которые сокращенно называли DMV (сноска: игра слов - DMV - это также Department of Motor Vehicles, автотранспортная инспекция). Возникли языки дизайна Verilog и VHDL и технология логического синтеза, которые вместе позволяли инженеру писать логические и математические выражения в виде текста, а не рисовать кропотливо сеть из логических элементов с помощью мышки на экране.

В 1990-х количество транзисторов на кристалле стало ограничиваться не возможностями станков на фабрике, а производительностью труда инженеров. После окончания «холодной войны» с СССР, главными клиентами EDA-компаний стали не военные, а производители потребительской электроники.

Дополнение 2 - Список рекомендуемой литературы:

Из учебников для самых начинающих лично мне больше всего понравилась David Harris, Sarah Harris. Digital Design and Computer Architecture.

Там есть и про логику, и про HDL, и введение в процессоры:

С этой книжкой можно просто взять в руки какой-нибудь бесплатный симулятор верилога - и вперед.

Также для самого-самого начала есть полезная книжка для "легкого чтения" с описанием работы дизайнеров для нетехнических людей (например маркетологов):

Essential Electronic Design Automation (EDA)

Mark D. Birnbaum

Есть также стандартная вводная книжка Patterson & Hennesy для студентов начальных курсов, но она ИМХО слишком многословная и разбавленная, кроме этого она более софтверная, чем хардверная, т.е. вначале слишком много ассемблера (для того кто уже знает, будет неинтересно):

David A. Patterson, John L. Hennessy. Computer Organization and Design, Fourth Edition: The Hardware/Software Interface.

Далее есть более продвинутая и тоже стандартная университетская книжка, но ИМХО не очень хорошо структурированная:

Computer Architecture: A Quantitative Approach, 4th Edition

John L. Hennessy, David A. Patterson

Занятная книженция с историческими статьями про изобретения тех или иных микропроцессорных штучек:

Readings in Computer Architecture (The Morgan Kaufmann Series in Computer Architecture and Design)

Mark D. Hill, Norman P. Jouppi, Gurindar S. Sohi

Вот есть еще новая книжка, которую я не читал, но судя по оглавлению,

там есть многие нужные вещи:

Microprocessor Architecture

Jean-Loup Baer

Для многих адванснутых штучек нужно читать университетские статьи. Например про многоядерность и когерентные кэши книг мало, зато статей на интернете самого разного уровня понятности - навалом.

Poll