Как делают микросхемы

01

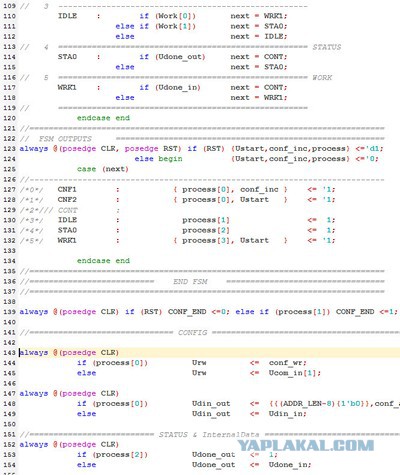

Микросхемы пишут на языке Verilog.

Примерно как программы для компов пишут на языках программирования C++ и прочих, так и процессоры для компов пишут на языках описания аппаратуры (HDL - hardware description language), например Verilog.

12 фотографий.

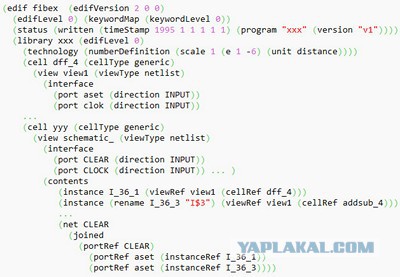

Он выглядит так:

Verilog

02

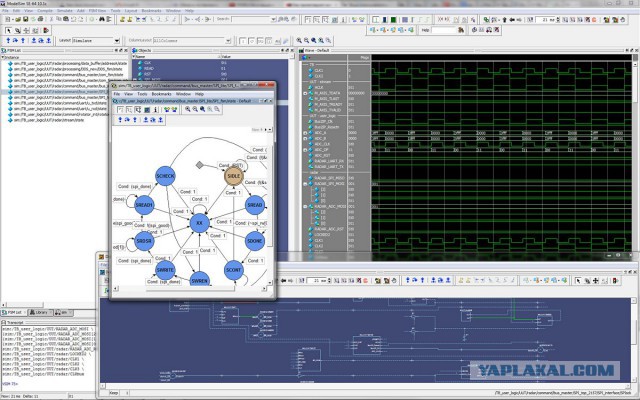

Исходный код на верилоге будущей микрухи долго отлаживается виртуально. Пишутся тесты, которые подают виртуальные сигналы на входы, просматриваются внутренние и выходные сигналы, прохождение данных, переходы по состояниям внутренних конечных автоматов (fsm - finite state machine), и подобное.

Это сообщение отредактировал LordOfSteel - 1.08.2014 - 18:39

Modelsim

03

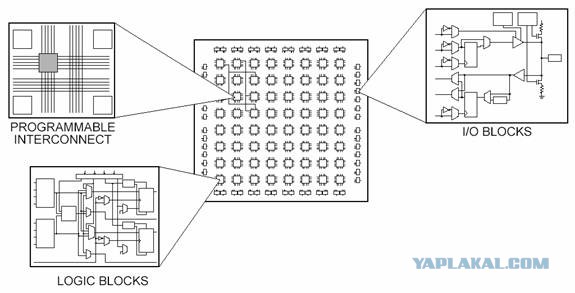

Исходный код будем транслировать в прошифку специальной микросхемы - FPGA. Это крутая микросхема field-programmable gate array.

Внутри fpga очень много маленьких простых логических блоков, которые можно запрограммировать на выполнение

какой-либо простой логической функции.

А ещё внутри fpga есть куча матриц соединений и трассировочных ресурсов, для соединения маленьких логических блоков в большие сложные логические структуры.

То есть внутри fpga есть много маленьких обломков логических микросхем, и средства соединения этих кусочков микросхем в одну большую микросхемищу, такую какую надо.

fpga

04

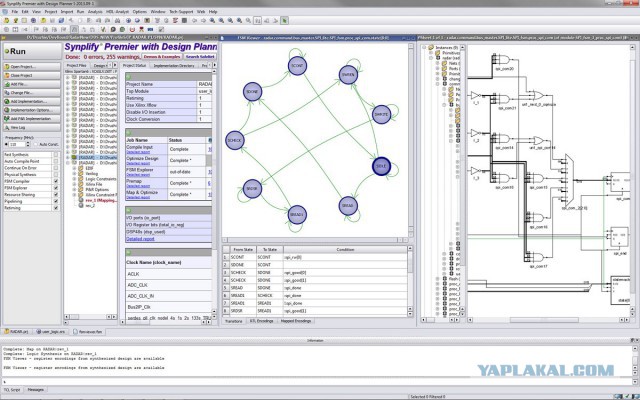

HDL исходники засовываются в синтезатор. Это типа компилятор у программистов. Синтезатор синтезирует код в микросхемообразное представление, делает логический синтез, позволяет посмотреть получающуюся схему RTL, состояния и переходы конечных автоматов.

Это сообщение отредактировал LordOfSteel - 1.08.2014 - 19:09

Synplify

05

Код на HDL синтезируется в так называемый netlist, он же нетлист. Это набор элементарных простых логических блоков и список соединений между ними в формате EDIF.

Это сообщение отредактировал LordOfSteel - 1.08.2014 - 19:10

netlist

06

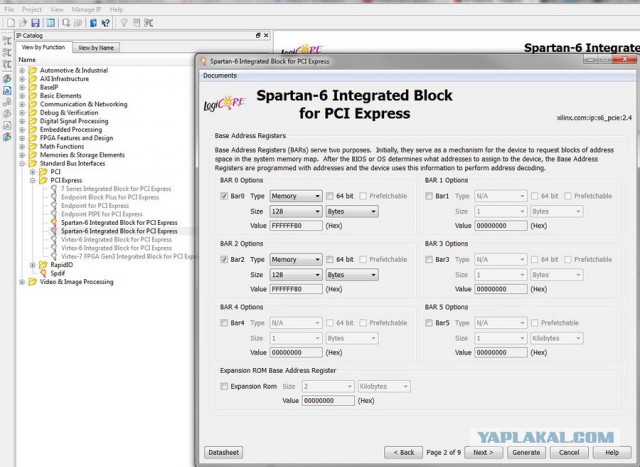

Добавляются готовые логические ip-ядра IP-cores.

Это готовые отлаженные куски кода или уже отсинтезированные нетлисты, предназначенные для выполнения какой-нибудь функции. На фотки ip-ядро PCI-Express.

Это сообщение отредактировал LordOfSteel - 1.08.2014 - 19:13

coregen

07

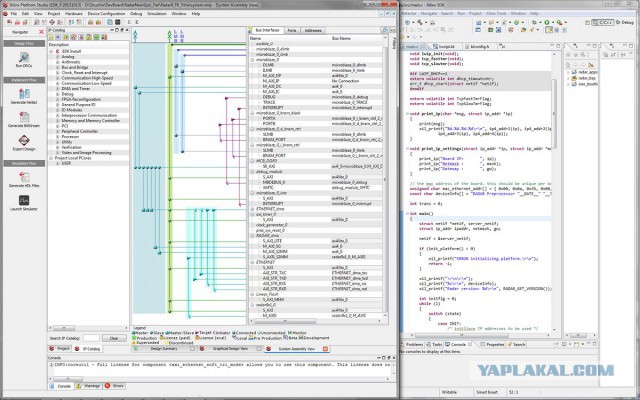

Прицепляем 32-х разрядное микропроцессорное ядро MicroBlaze Soft Processor, для которого пишем софт на C++.

microblaze

08

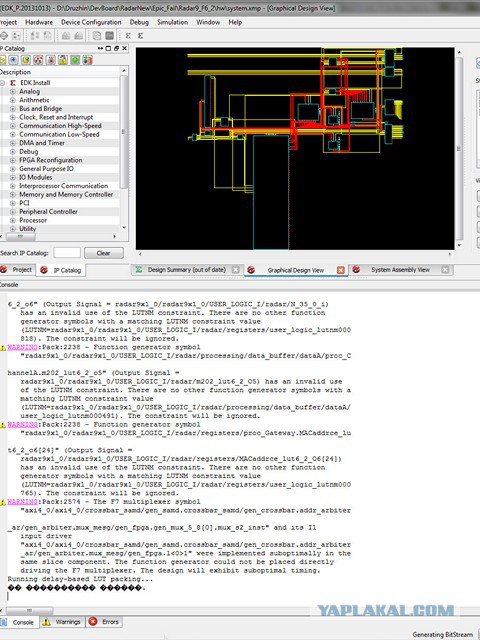

Дальше запускается долгий процесс Implementation, засовывание в раскладывание в FPGA логических функций по логическим ячейкам и соединение ячеек в нужную структуру.

par

09

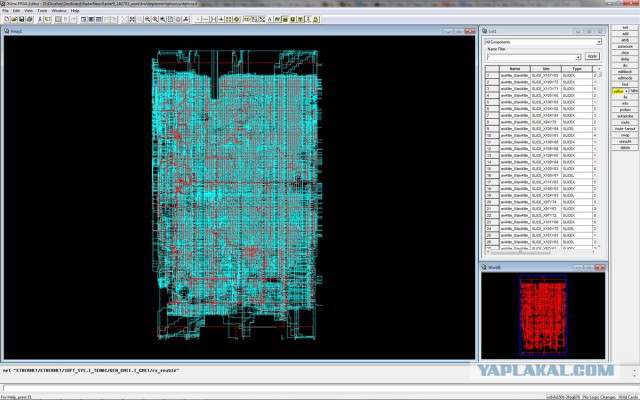

Результат выглядит так. Это схема FPGA с соединениями.

fpga editor 1

10

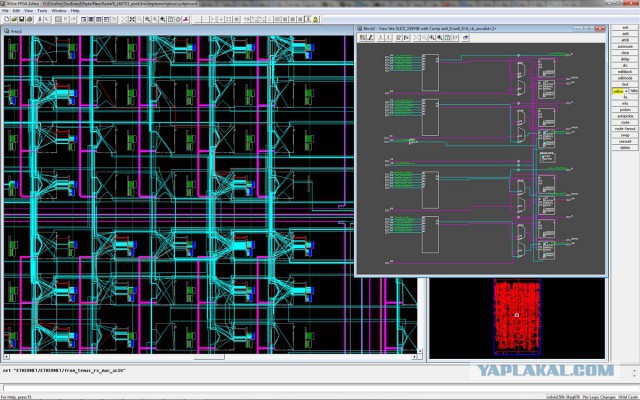

Немного увеличим. Так выглядят логические ячейки CLB (Configurable Logic Block) с соединениями. Справа вверху схема одного CLB.

Это сообщение отредактировал LordOfSteel - 1.08.2014 - 18:39

fpga editor 2

11

Результат заливаем в FPGA для аппаратной отладки на отладочной плате.

hard 1

12

Готовое изделие.

В реальности всё намного сложнее, используется огромная куча софта.

Приходится писать и править кучу файлов разных форматов.

ВСЁ.

hard 2