Исходники промышленных процессоров станут доступными для университетов

Кто помнит серию постов «Как пересечь пропасть от физики к программированию», в лабораторной работе 5 мы делали реализацию сильно урезанного и максимально упрощенного процессора MIPS (7 команд из более сотни) и запускали его на ПЛИС, а в следующей работе знакомились с его промышленной реализацией в виде чипа PIC32MX.

Теперь у студентов и преподавателей вузов, которые захотят принять участие в новой образовательной программе Imagination Technologies, появится возможность полностью заполнить расстояние между этими двумя лабами, получив полные исходники промышленного ядра PIC32MZ (самое новое в линейке PIC32, на данный момент топовое в классе микроконтроллеров) на языке Verilog, пригодные для запуска на той же ПЛИС.

Мои мысли, кому это может быть интересно помимо несомненной образовательной пользы из беседы в фейсбуке:

Александр Крот: Антон, а можешь в двух словах обьяснить непосвященным? Поверхностно проглядел - не понимаю, как это связано с образованием и в чем революция?)

Anton Moiseev: В двух словах боюсь, не получится, но постараюсь доступно. Сейчас, если говорить о попсовых решениях в микроэлектронике лично ты (инженер-любитель без сотен бюджета, не работающий в спецконторе) обычно выбираешь или микроконтроллер сначала из короткого списка архитектур x86,ARM,MIPS,AVR, потом под архитектуру чуть длиннее список конкретных чипов с параметрами быстродействие/память и т.п., потом может быть еще и удобную плату с периферией - в этом случае ты работаешь чисто с софтом, как обычный программист. Но в некоторых задачах тебе может захотеться выйти за пределы контроллера и реально в тысячи раз ускорить какой-нибудь алгоритм при помощи специализированного аппаратного решения (я могу представить себе такие задачи с распространением разных автономных устройств типа роботов и носимой электроники). В этом случае тебе, как "любителю" без сотен бюджета, доступны такие штуки, которые называются ПЛИС - это аппаратное обеспечение, структуру которого можно менять налету примерно как прошивку микроконтроллера (на создание специализированных микросхем ASIC у тебя не хватит денег). Мир ПЛИС можно сказать есть некий промежуточный этап между этапом разработки чипов и их серийным производством, но их можно использовать и сами по себе как дешевую достпную платформу для аппаратных решений, которые на некоторых специальных задачах все равно будут рвать контроллеры общего назначения. Причем прошивка для ПЛИС создается на языке описания аппаратного обеспечения (VHDL или Verilog), на этом же языке описываются чипы, которые могут быть воспроизведены как ASIC, т.е. переход ПЛИС->ASIC довольно размыт и органичен, в то время как между СОФТ-на-контроллере->ASIC лежит огромная пропасть. Если помнишь историю с биткоинами, то сначала были программные майнеры, потом майнеры на ПЛИС, потом уже специализированные чипы ASIC.

Дальше, при всех преимуществах, на ПЛИС ты все равно всю прошивку для своей системы не перетащишь - есть спецзадачи, которые получат реальный выигрыш от аппаратного ускорения (твое аппаратное ноу-хау), а есть куча сервисных задач общего назначения (операционка, драйверы устройств, тысячи внешних библиотек), без которых ты не сделаешь сколько-нибудь функционального решения, и без контроллера ты с ними один фиг не обойдешься. Обычное решение здесь - городить огород, объединяя ПЛИС и контроллер на одной плате - нормальное рабочее решение, но может породить ряд технических ограничений и дополнительных сложностей. Другой вариант - затащить на ПЛИС контроллер общего назначения целиком и гонять на нем и софтверные задачи общего назначения и свой спец-алгоритм рядом, вообще не запариваясь о том, как их между собой связывать (например, можешь просто добавить новую команду в ассемблер). До сего момента на ПЛИС существовало некоторое количество открытых полулюбительских ядер общего назначение, которые, однако, не могли похвастаться распространенностью (ядро - это не только его технические характеристики, но и тонны софта и библиотек, которые для него скомпилированы, сообщество разработчиков и т.п.).

Вот здесь и появляется МИПС со своей инициативой - сейчас они притащили в эту среду полулюбительских аппаратно-программных решений ядро промышленного класса (PIC32MZ ряд авторитетов назвали топовым в классе микроконтроллеров) и дали к нему доступ большому количеству людей, которые ранее к такого рода решениям доступ не имели. Размывается граница между миров алгоритмов и программирования и миром аппаратных решений.

Т.е. если ты например студент-математик-программист, придумал какой-нибудь алгоритм распознавания образов в реальном времени, который порвет рынок решений машинного зрения, ты сможешь теперь тихо никого не спрашивая не просто обкатать его на ПЛИС, но и построить на его основе законченное решение в связке с контроллером промышленного класса, от которого до коммерциализации в ASIC или в том же ПЛИС будет один шаг. В современном мире для того, чтобы получить аналогичный результат, тебе придется просить дядей, купивших доступ к таким исходникам, уже на этапе разработки, равносильно никакая разработка не состоится.

(добавил) Anton Moiseev: В двух словах - размытие границы между процессом создания программного обеспечения и аппаратного обеспечения: сидишь пишешь такой код для обычного контроллера на обычном Си, вдруг бах, решил добавить новую команду в ассемблер - запилил несколько строк на Верилоге, мышкой отправил прошивку на ПЛИС и все, у тебя новый процессор, заточенный под твою индивидуальную задачу. Как говорил Степан Большедворский, "Каждый программист будет делать процессор под себя" - ночной кошмар Алекса Экслера

Оригинал взят у panchul в Исходники промышленных процессоров станут доступными для университетов

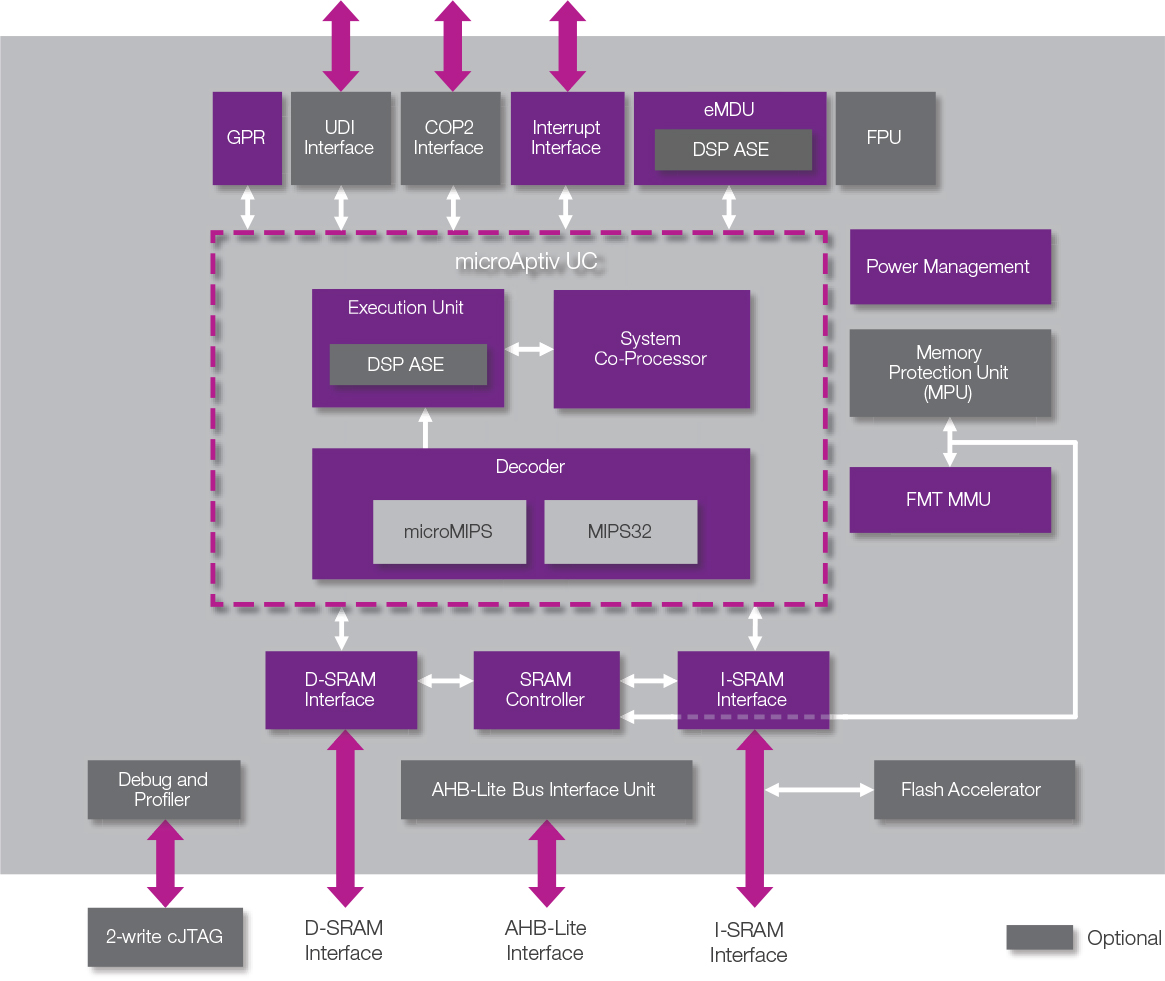

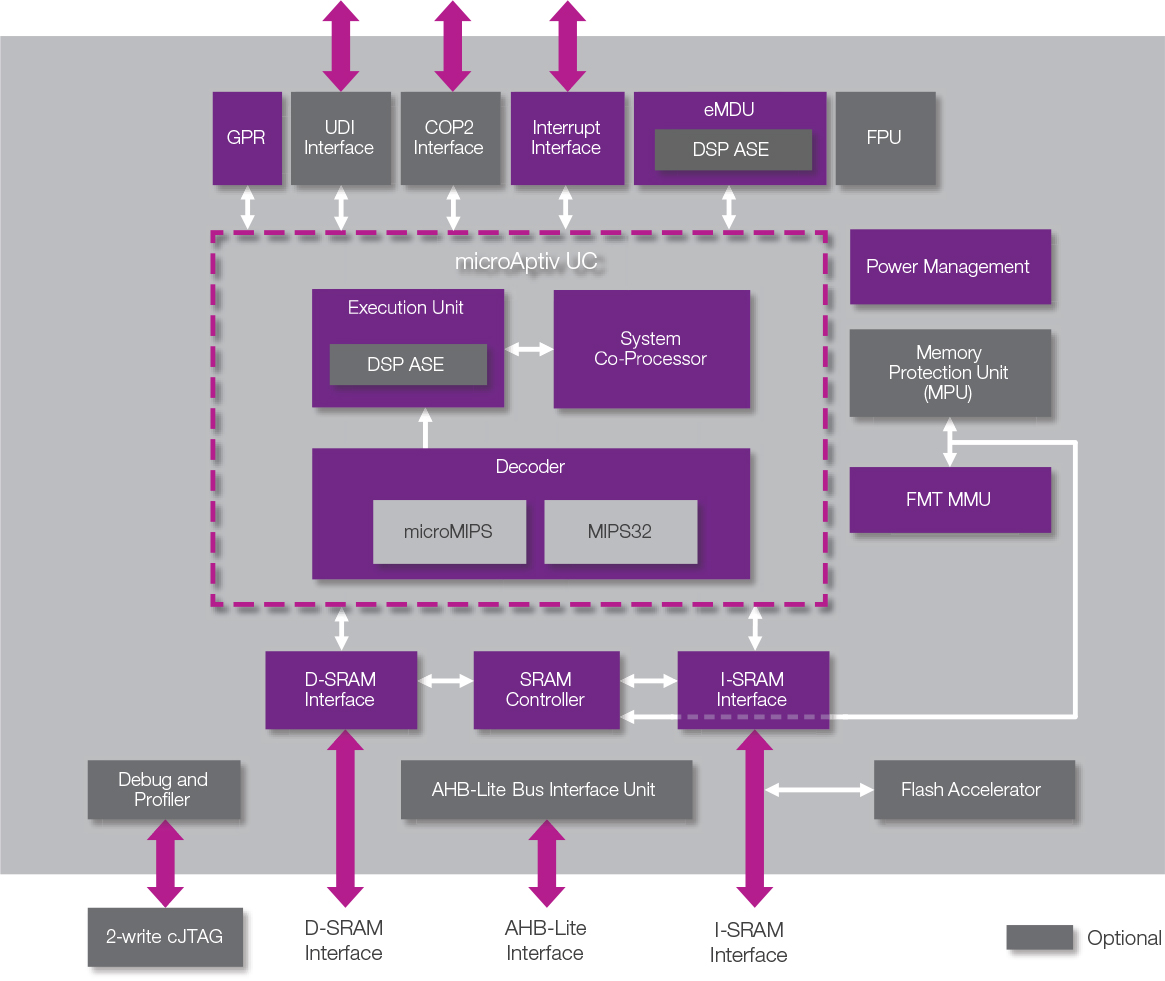

Господа! На днях Imagination Technologies (компания, которая спроектировала графический процессор PowerVR GPU внутри Apple iPhone) и Xilinx (компания №1 в ПЛИС-ах / FPGA) начали понемногу предавать гласности несколько иконоборческую инициативу по бесплатной раздаче университетам исходников современного индустриального процессорного ядра MIPS microAptiv UP, которое используется например в микроконтроллере Microchip PIC32MZ. Студенты смогут менять команды этого процессора, добавлять к нему свои периферийные устройства и реализовывать полученный дизайн на ПЛИС-ах.

Вот линк на сообщение о семинаре 13-14 мая возле Лос-Анжелеса, на котором Imagination и Xilinx будет показывать новый продукт под названием MIPSfpga представителям academia - http://imgtec.com/mipsfpga

Фактически MIPSfpga - это бесплатная лицензия на базовую конфигурацию экономичного процессорного ядра MIPS microAptiv UP, которое предоставляется в исходных текстах на языке описания аппаратуры Verilog. Это то же самое ядро, которое продается коммерческим клиентам за сотни тысяч долларов. MIPS microAptiv UP - это простой дизайн с пятью стадиями последовательного конвейера (как в учебниках компьютерной архитектуры), но в нем есть кэши и TLB MMU. TLB MMU позволяет даже использовать на нем Линукс.

Описание ядра: http://www.imgtec.com/mips/aptiv/microaptiv.asp

Наиболее широко известным примером использования ядра MIPS microAptiv UP является 32-битный микроконтроллер Microchip PIC32MZ, который начали выпускать в прошлом году. А из самых последних примеров использования: 10 апреля этого года Electronic Engineering Times опубликовала статью про южнокорейский стартап Standing Egg, который лицензировал ядро MIPS M5100 (фактически MIPS microAptiv без кэшей и MMU, но с добавленным расширением для виртуализации) для создания платформы для MEMS сенсоров, с приложениями для Internet of Things:

http://www.eetimes.com/document.asp?doc_id=1326327

Разработчики микросхем с MIPS microAptiv UP используют стандартную за последние 20 лет методологию электронного дизайна под названием Register Transfer Level (RTL, уровень регистровых передач). Согласно этой методологии, дизайн пишется на языке Verilog, после чего специальная программа (logic synthesis) превращает дизайн в граф из проводов и логических элементов, другая программа (static timing analysis) сообщает разработчику, вписывается ли он в бюджет скорости, а третья программа (place-and-route) раскладывает этот дизайн по площадке микросхемы.

Когда дизайн проходит все этапы: кодирование на верилоге, отладка, верификация, синтез, static timing analysis, floorplanning, place-n-route, parasitics extraction и т.д. - получается файл под названием GDSII, который отправляют на фабрику, где и изготавливаются микросхемы. Самые известные фабрики этого типа принадлежат компании Taiwan Semiconductor Manufacturing Company или TSMC. При этом, ничего не мешает производить микросхемы с ядром MIPS microAptiv UP на российских фабриках Микрон и Ангстрем.

Альтернативой производству микросхемы на фабрике является реализация дизайна на программируемых пользователем матрицах логических элементов (Field Programmable Gate Array - FPGA), что и используется для образовательных целей в новом продукте MIPSfpga.

Хотя пакет MIPSfpga и заточен на синтез для FPGA (например в MIPSfpga есть реализация памяти внутри кэшей, используя макро для Xilinx Artix-7 и Altera Cyclone IV), но в основном это те же исходники, которые используются и для синтеза в ASIC. Иными словами, студенты и аспиранты могут экспериментировать с ядром на недорогих FPGA-платах, придумать какое-нибудь интересное решение (скажем многоядерную SoC из малых некогерентных ядер, или комбинацию из ядра MIPS microAptiv UP со специализированным студенческим DSP процессором), не вкладывая при этом денег инвесторов, после чего, когда идея доказана, найти инвесторов, приобрести коммерческую лицензию и сделать микросхему на фабрике - ASIC.

Обращаю внимание, что в случае с MIPSfpga речь идет не об ограниченном образовательном подмножестве MIPS (таких подножеств довольно много из других источников) и не об open-source ядре типа OpenRISC или Leon4, а о коммерчески успешном современном индустриальном ядре, которое за деньги лицензировало несколько десятков компаний.

У конкурирующей компании ARM тоже есть soft core для образовательного экспериментирования на FPGA, но их ядро не в открытом исходном тексте (т.е. студенты не могут подключать провода к внутренним регистрам и модифицировать верилог), у ARM-овского ядра ARM Cortex M0 в конкурирующем продукте нет кэшей, интерфейса к отладчику и TLB MMU. Все это у MIPSfpga есть.

Дополнительные детали:

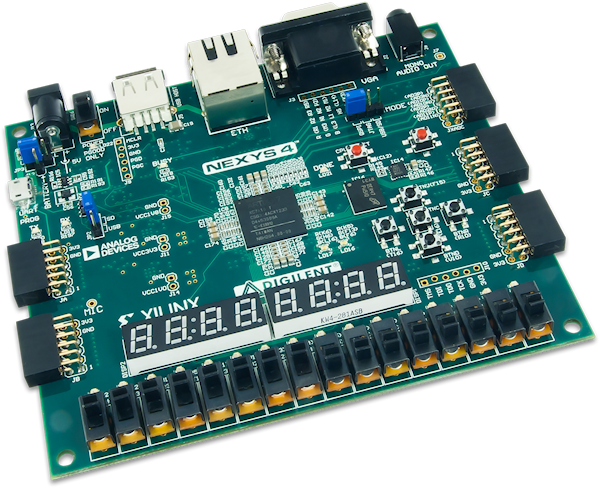

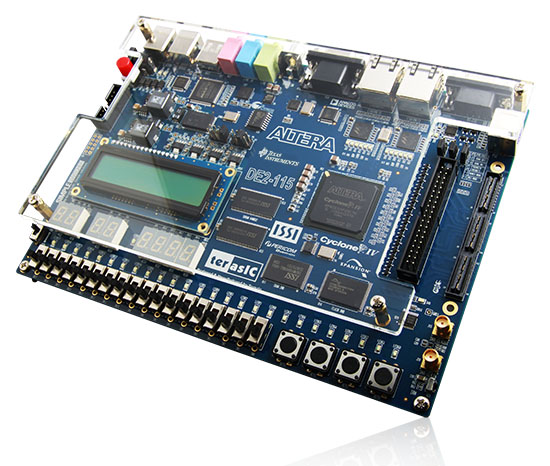

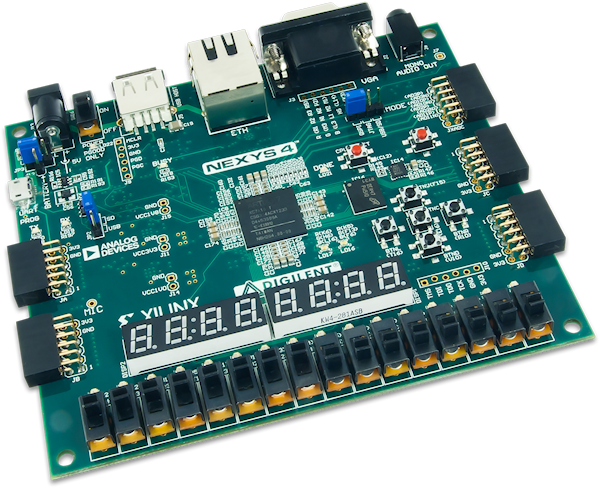

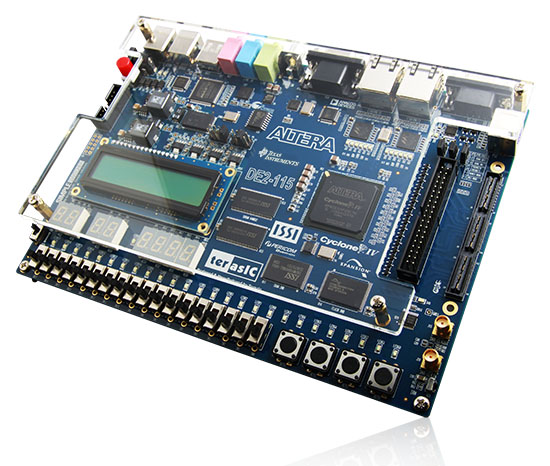

Сейчас MIPSfpga работает на двух платах Digilent Nexys-4 с Xilinx Artix-7 и Altera DE2-115 с Cyclone IV E. У первой академическая цена $180 / коммерческая $320, у второй академическая $300 / коммерческая $600. Перенести его на другие платы довольно легко (при условии, что вместится) - нужно заменить некоторые макро для памяти и подсоединить top-module к board-specific внешнему verilog wrapper-у. В частности, можно попробовать перенести его на дешевую плату Digilent Basys-3 с Xilinx Artix-7 (академическая $80 / коммерческая $150), а также на платы, которые спроектированы или производятся в России.

В качестве toolchain предлагается Codescape MIPS SDK, который содержит отладчик и GCC toolchain. Связь между отладчиком и платой Nexys-4 делается с помощью EJTAG, BusBlaster probe и OpenOCD. На Altera DE2 115 применяется отладочный интерфейс который стоит прямо на плате, т.е. BusBlaster не нужен. Также прилагается Boot code на ассемблере, который инициализирует кэши и MMU и т.д.

Теперь какое это может иметь отношение к вам:

1. Первый этап апробации MIPSfpga на трех университетах в US и UK успешно завершен. Теперь продукт будет проходить бета-тестирование в бОльшем количестве университетов в США, Европе и Азии. Если вы работаете в университете, и в нем есть достаточная экспертиза в Verilog или VHDL чтобы работать с пакетом, то вы можете принять участие как early adopter и получить преимущество перед другими вузами в его использовании.

2. 13-14 мая в Лос-Анжелесе будет проходить семинар, организованный Imagination Technologies вместе с Xilinx, на котором профессора Harvey Mudd College и application engineers из Imagination будут тренировать профессоров различных вузов использовать MIPSfpga. Если вы или кто-либо из ваших знакомых преподавателей уиверситетов хочет в нем участвовать и может приехать в это время в Лос-Анжелес, просьба связаться либо с менеджером образовательных программ Робертом Оуэном (его координаты в http://imgtec.com/mipsfpga ), либо со мной (yuri.panchul@imgtec.com).

3. К моменту семинара в Лос-Анжелесе MIPSfpga будет официально объявлен, а после завершения (1) станет общедоступным. Поэтому если вы не имеете возможности принять участие как early adopter, вы тем не менее сможете начать работать с продуктом летом.

Возможность использования индустриальных процессорных ядер на верилоге в образовательных целях и без покупки коммерческой лицензии, позволит большому числу молодых разработчиков в academia заняться прототипированием инноваторских решений в области систем на кристалле и расширений микроархитектуры, с непосредственным путем к коммерциализации - созданию своих микросхем для интернета вещей и других приложений.

Юрий Панчул

Senior Hardware Design Engineer, MIPS processors

Imagination Technologies

Этот текст я сначала написал для http://habrahabr.ru : Исходники промышленных процессоров станут доступными для университетов

Poll

Теперь у студентов и преподавателей вузов, которые захотят принять участие в новой образовательной программе Imagination Technologies, появится возможность полностью заполнить расстояние между этими двумя лабами, получив полные исходники промышленного ядра PIC32MZ (самое новое в линейке PIC32, на данный момент топовое в классе микроконтроллеров) на языке Verilog, пригодные для запуска на той же ПЛИС.

Мои мысли, кому это может быть интересно помимо несомненной образовательной пользы из беседы в фейсбуке:

Александр Крот: Антон, а можешь в двух словах обьяснить непосвященным? Поверхностно проглядел - не понимаю, как это связано с образованием и в чем революция?)

Anton Moiseev: В двух словах боюсь, не получится, но постараюсь доступно. Сейчас, если говорить о попсовых решениях в микроэлектронике лично ты (инженер-любитель без сотен бюджета, не работающий в спецконторе) обычно выбираешь или микроконтроллер сначала из короткого списка архитектур x86,ARM,MIPS,AVR, потом под архитектуру чуть длиннее список конкретных чипов с параметрами быстродействие/память и т.п., потом может быть еще и удобную плату с периферией - в этом случае ты работаешь чисто с софтом, как обычный программист. Но в некоторых задачах тебе может захотеться выйти за пределы контроллера и реально в тысячи раз ускорить какой-нибудь алгоритм при помощи специализированного аппаратного решения (я могу представить себе такие задачи с распространением разных автономных устройств типа роботов и носимой электроники). В этом случае тебе, как "любителю" без сотен бюджета, доступны такие штуки, которые называются ПЛИС - это аппаратное обеспечение, структуру которого можно менять налету примерно как прошивку микроконтроллера (на создание специализированных микросхем ASIC у тебя не хватит денег). Мир ПЛИС можно сказать есть некий промежуточный этап между этапом разработки чипов и их серийным производством, но их можно использовать и сами по себе как дешевую достпную платформу для аппаратных решений, которые на некоторых специальных задачах все равно будут рвать контроллеры общего назначения. Причем прошивка для ПЛИС создается на языке описания аппаратного обеспечения (VHDL или Verilog), на этом же языке описываются чипы, которые могут быть воспроизведены как ASIC, т.е. переход ПЛИС->ASIC довольно размыт и органичен, в то время как между СОФТ-на-контроллере->ASIC лежит огромная пропасть. Если помнишь историю с биткоинами, то сначала были программные майнеры, потом майнеры на ПЛИС, потом уже специализированные чипы ASIC.

Дальше, при всех преимуществах, на ПЛИС ты все равно всю прошивку для своей системы не перетащишь - есть спецзадачи, которые получат реальный выигрыш от аппаратного ускорения (твое аппаратное ноу-хау), а есть куча сервисных задач общего назначения (операционка, драйверы устройств, тысячи внешних библиотек), без которых ты не сделаешь сколько-нибудь функционального решения, и без контроллера ты с ними один фиг не обойдешься. Обычное решение здесь - городить огород, объединяя ПЛИС и контроллер на одной плате - нормальное рабочее решение, но может породить ряд технических ограничений и дополнительных сложностей. Другой вариант - затащить на ПЛИС контроллер общего назначения целиком и гонять на нем и софтверные задачи общего назначения и свой спец-алгоритм рядом, вообще не запариваясь о том, как их между собой связывать (например, можешь просто добавить новую команду в ассемблер). До сего момента на ПЛИС существовало некоторое количество открытых полулюбительских ядер общего назначение, которые, однако, не могли похвастаться распространенностью (ядро - это не только его технические характеристики, но и тонны софта и библиотек, которые для него скомпилированы, сообщество разработчиков и т.п.).

Вот здесь и появляется МИПС со своей инициативой - сейчас они притащили в эту среду полулюбительских аппаратно-программных решений ядро промышленного класса (PIC32MZ ряд авторитетов назвали топовым в классе микроконтроллеров) и дали к нему доступ большому количеству людей, которые ранее к такого рода решениям доступ не имели. Размывается граница между миров алгоритмов и программирования и миром аппаратных решений.

Т.е. если ты например студент-математик-программист, придумал какой-нибудь алгоритм распознавания образов в реальном времени, который порвет рынок решений машинного зрения, ты сможешь теперь тихо никого не спрашивая не просто обкатать его на ПЛИС, но и построить на его основе законченное решение в связке с контроллером промышленного класса, от которого до коммерциализации в ASIC или в том же ПЛИС будет один шаг. В современном мире для того, чтобы получить аналогичный результат, тебе придется просить дядей, купивших доступ к таким исходникам, уже на этапе разработки, равносильно никакая разработка не состоится.

(добавил) Anton Moiseev: В двух словах - размытие границы между процессом создания программного обеспечения и аппаратного обеспечения: сидишь пишешь такой код для обычного контроллера на обычном Си, вдруг бах, решил добавить новую команду в ассемблер - запилил несколько строк на Верилоге, мышкой отправил прошивку на ПЛИС и все, у тебя новый процессор, заточенный под твою индивидуальную задачу. Как говорил Степан Большедворский, "Каждый программист будет делать процессор под себя" - ночной кошмар Алекса Экслера

Оригинал взят у panchul в Исходники промышленных процессоров станут доступными для университетов

Господа! На днях Imagination Technologies (компания, которая спроектировала графический процессор PowerVR GPU внутри Apple iPhone) и Xilinx (компания №1 в ПЛИС-ах / FPGA) начали понемногу предавать гласности несколько иконоборческую инициативу по бесплатной раздаче университетам исходников современного индустриального процессорного ядра MIPS microAptiv UP, которое используется например в микроконтроллере Microchip PIC32MZ. Студенты смогут менять команды этого процессора, добавлять к нему свои периферийные устройства и реализовывать полученный дизайн на ПЛИС-ах.

Вот линк на сообщение о семинаре 13-14 мая возле Лос-Анжелеса, на котором Imagination и Xilinx будет показывать новый продукт под названием MIPSfpga представителям academia - http://imgtec.com/mipsfpga

Фактически MIPSfpga - это бесплатная лицензия на базовую конфигурацию экономичного процессорного ядра MIPS microAptiv UP, которое предоставляется в исходных текстах на языке описания аппаратуры Verilog. Это то же самое ядро, которое продается коммерческим клиентам за сотни тысяч долларов. MIPS microAptiv UP - это простой дизайн с пятью стадиями последовательного конвейера (как в учебниках компьютерной архитектуры), но в нем есть кэши и TLB MMU. TLB MMU позволяет даже использовать на нем Линукс.

Описание ядра: http://www.imgtec.com/mips/aptiv/microaptiv.asp

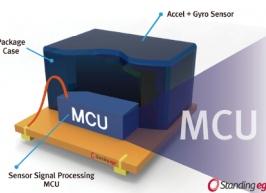

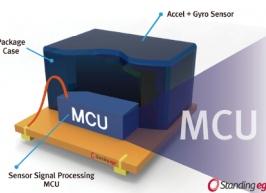

Наиболее широко известным примером использования ядра MIPS microAptiv UP является 32-битный микроконтроллер Microchip PIC32MZ, который начали выпускать в прошлом году. А из самых последних примеров использования: 10 апреля этого года Electronic Engineering Times опубликовала статью про южнокорейский стартап Standing Egg, который лицензировал ядро MIPS M5100 (фактически MIPS microAptiv без кэшей и MMU, но с добавленным расширением для виртуализации) для создания платформы для MEMS сенсоров, с приложениями для Internet of Things:

http://www.eetimes.com/document.asp?doc_id=1326327

Разработчики микросхем с MIPS microAptiv UP используют стандартную за последние 20 лет методологию электронного дизайна под названием Register Transfer Level (RTL, уровень регистровых передач). Согласно этой методологии, дизайн пишется на языке Verilog, после чего специальная программа (logic synthesis) превращает дизайн в граф из проводов и логических элементов, другая программа (static timing analysis) сообщает разработчику, вписывается ли он в бюджет скорости, а третья программа (place-and-route) раскладывает этот дизайн по площадке микросхемы.

Когда дизайн проходит все этапы: кодирование на верилоге, отладка, верификация, синтез, static timing analysis, floorplanning, place-n-route, parasitics extraction и т.д. - получается файл под названием GDSII, который отправляют на фабрику, где и изготавливаются микросхемы. Самые известные фабрики этого типа принадлежат компании Taiwan Semiconductor Manufacturing Company или TSMC. При этом, ничего не мешает производить микросхемы с ядром MIPS microAptiv UP на российских фабриках Микрон и Ангстрем.

Альтернативой производству микросхемы на фабрике является реализация дизайна на программируемых пользователем матрицах логических элементов (Field Programmable Gate Array - FPGA), что и используется для образовательных целей в новом продукте MIPSfpga.

Хотя пакет MIPSfpga и заточен на синтез для FPGA (например в MIPSfpga есть реализация памяти внутри кэшей, используя макро для Xilinx Artix-7 и Altera Cyclone IV), но в основном это те же исходники, которые используются и для синтеза в ASIC. Иными словами, студенты и аспиранты могут экспериментировать с ядром на недорогих FPGA-платах, придумать какое-нибудь интересное решение (скажем многоядерную SoC из малых некогерентных ядер, или комбинацию из ядра MIPS microAptiv UP со специализированным студенческим DSP процессором), не вкладывая при этом денег инвесторов, после чего, когда идея доказана, найти инвесторов, приобрести коммерческую лицензию и сделать микросхему на фабрике - ASIC.

Обращаю внимание, что в случае с MIPSfpga речь идет не об ограниченном образовательном подмножестве MIPS (таких подножеств довольно много из других источников) и не об open-source ядре типа OpenRISC или Leon4, а о коммерчески успешном современном индустриальном ядре, которое за деньги лицензировало несколько десятков компаний.

У конкурирующей компании ARM тоже есть soft core для образовательного экспериментирования на FPGA, но их ядро не в открытом исходном тексте (т.е. студенты не могут подключать провода к внутренним регистрам и модифицировать верилог), у ARM-овского ядра ARM Cortex M0 в конкурирующем продукте нет кэшей, интерфейса к отладчику и TLB MMU. Все это у MIPSfpga есть.

Дополнительные детали:

Сейчас MIPSfpga работает на двух платах Digilent Nexys-4 с Xilinx Artix-7 и Altera DE2-115 с Cyclone IV E. У первой академическая цена $180 / коммерческая $320, у второй академическая $300 / коммерческая $600. Перенести его на другие платы довольно легко (при условии, что вместится) - нужно заменить некоторые макро для памяти и подсоединить top-module к board-specific внешнему verilog wrapper-у. В частности, можно попробовать перенести его на дешевую плату Digilent Basys-3 с Xilinx Artix-7 (академическая $80 / коммерческая $150), а также на платы, которые спроектированы или производятся в России.

В качестве toolchain предлагается Codescape MIPS SDK, который содержит отладчик и GCC toolchain. Связь между отладчиком и платой Nexys-4 делается с помощью EJTAG, BusBlaster probe и OpenOCD. На Altera DE2 115 применяется отладочный интерфейс который стоит прямо на плате, т.е. BusBlaster не нужен. Также прилагается Boot code на ассемблере, который инициализирует кэши и MMU и т.д.

Теперь какое это может иметь отношение к вам:

1. Первый этап апробации MIPSfpga на трех университетах в US и UK успешно завершен. Теперь продукт будет проходить бета-тестирование в бОльшем количестве университетов в США, Европе и Азии. Если вы работаете в университете, и в нем есть достаточная экспертиза в Verilog или VHDL чтобы работать с пакетом, то вы можете принять участие как early adopter и получить преимущество перед другими вузами в его использовании.

2. 13-14 мая в Лос-Анжелесе будет проходить семинар, организованный Imagination Technologies вместе с Xilinx, на котором профессора Harvey Mudd College и application engineers из Imagination будут тренировать профессоров различных вузов использовать MIPSfpga. Если вы или кто-либо из ваших знакомых преподавателей уиверситетов хочет в нем участвовать и может приехать в это время в Лос-Анжелес, просьба связаться либо с менеджером образовательных программ Робертом Оуэном (его координаты в http://imgtec.com/mipsfpga ), либо со мной (yuri.panchul@imgtec.com).

3. К моменту семинара в Лос-Анжелесе MIPSfpga будет официально объявлен, а после завершения (1) станет общедоступным. Поэтому если вы не имеете возможности принять участие как early adopter, вы тем не менее сможете начать работать с продуктом летом.

Возможность использования индустриальных процессорных ядер на верилоге в образовательных целях и без покупки коммерческой лицензии, позволит большому числу молодых разработчиков в academia заняться прототипированием инноваторских решений в области систем на кристалле и расширений микроархитектуры, с непосредственным путем к коммерциализации - созданию своих микросхем для интернета вещей и других приложений.

Юрий Панчул

Senior Hardware Design Engineer, MIPS processors

Imagination Technologies

Этот текст я сначала написал для http://habrahabr.ru : Исходники промышленных процессоров станут доступными для университетов

Poll