Ардуина с ПЛИСом и Верилогом: предварительно

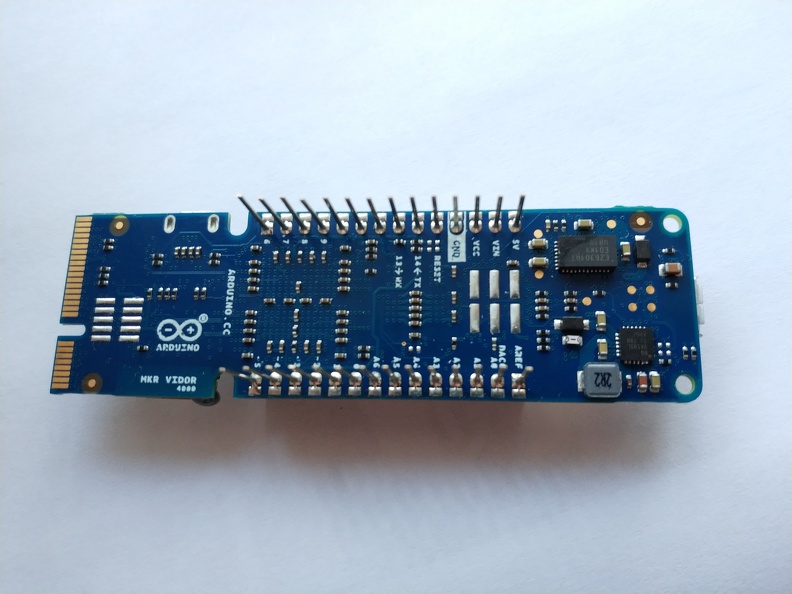

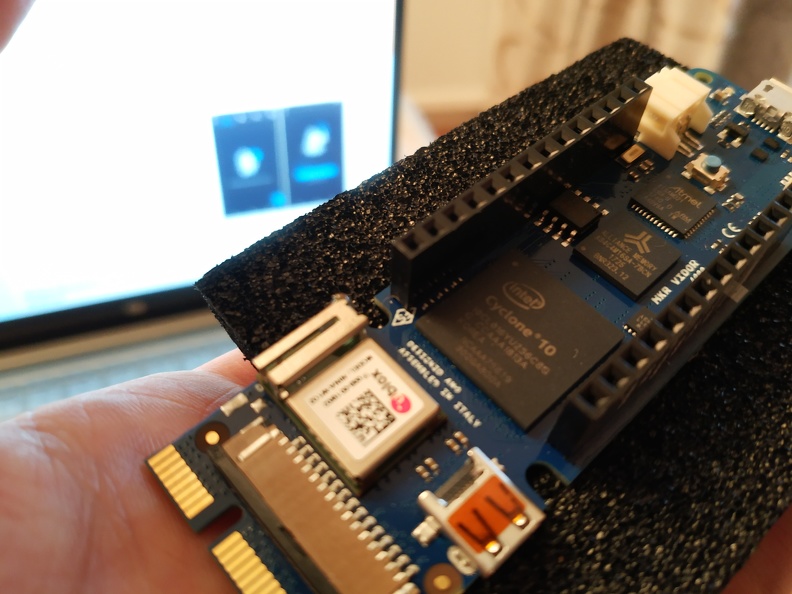

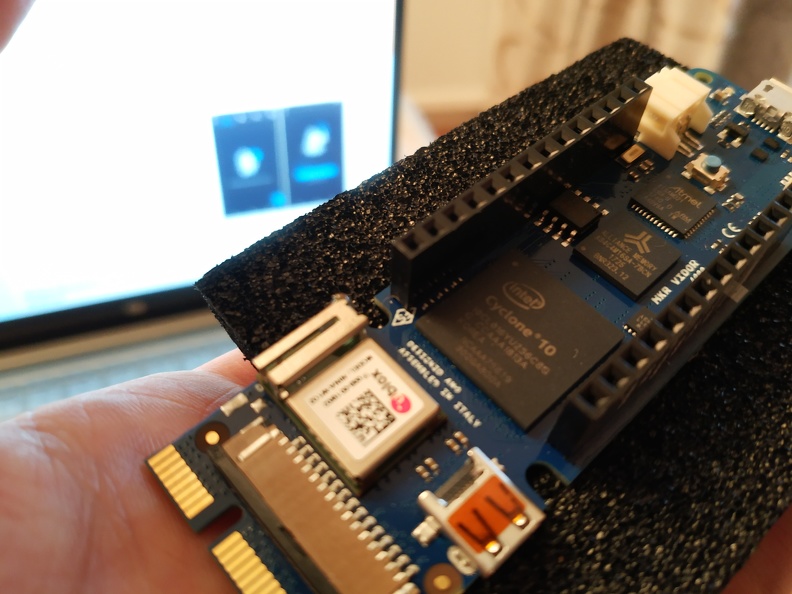

Предварительно по гибриду Ардуины и ПЛИСа (Arduino MKR Vidor 4000), репост из фейсбука

1. Самое интересное: прошивка для ПЛИС создается в обычном квартусе (Intel Quartus, бесплатная версия Lite), на обычном Верилоге, к среде Ардуино эта процедура никакого отношения не имеет. Из кода на верилоге Квартус генерирует файл ttf (так называемый битстрим), он дальше пойдет на ПЛИС несколькими возможными путями.

шаблон пустого проекта с топ-левел модулем, настройками и кое-какими ip-блоками (открывается, собирается, генерирует файл ttf в последнем Квартусе, проверил) здесь:

https://github.com/vidor-libraries/VidorFPGA

важный нюанс: на самом деле файл ttf, генерируемый Квартусом, как есть не подходит для прошивки чипа в плате, его предварительно нужно пропустить еще через некий постпроцессор, который производит с ним какие-то вспомогательные манипуляции. Сейчас этот инструмент не открыт, поэтому сгенерить свою прошивку из Верилога для платы вот прям сейчас не получится. Но обещают все открыть в обозримом (по словам разработчиков - в ближайшем) будущем. Можно немного подождать или попробовать сделать такой пост-процессор самостоятельно - на форуме и в статьях были кое-какие подробности, плюс можно поковырять файлы ttf, выложенные в качестве демо.

доб1: пост в фб 6 сентябня, сейчас 12 октября, вериложный тулчейн еще не открыт

доб2: когда (и если) все-таки откроют, будет повод вернуться к Верилогу

доб3: Альтера уже Интел

доб4: (из коментов) еще один производитель ПЛИС (не Xilinx и не Интел-Альтера) - Lattice: http://www.latticesemi.com/en/Products.aspx#_58F82ED81585418A93A8EE6349B10899

доб5: (из коментов) проект IceStorm - открытые утилиты для работы с ПЛИС Lattice (реверс-инжиниринг): http://www.clifford.at/icestorm/

АПДЕЙТ: 24 ноября, тулчейн открыли

https://forum.arduino.cc/index.php?PHPSESSID=a5hp71v7ioivdcl67hno0nurc2&topic=581316.0

https://github.com/vidor-libraries/VidorBitstream

2. Далее к этой прошивке ПЛИС создается обертка в виде библиотеки на С++. Она общается с ПЛИС (с конкретным дизайном, который туда зашит).

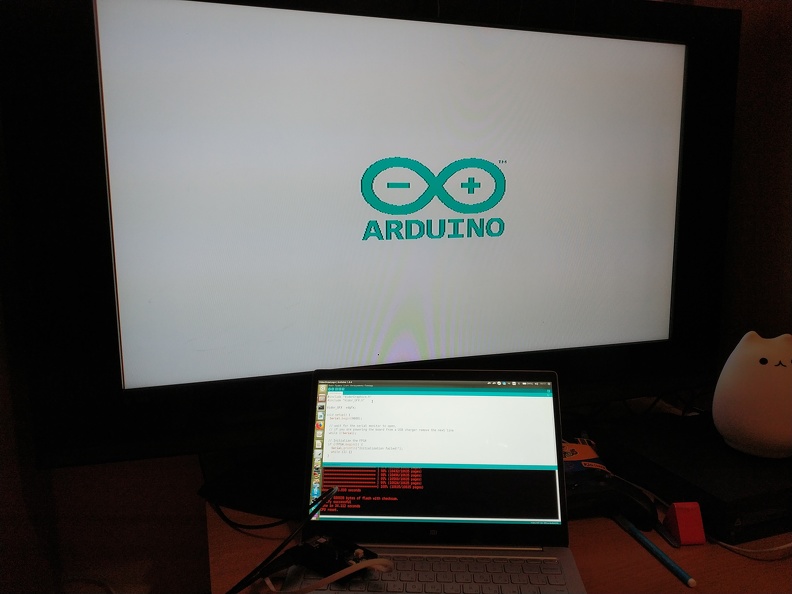

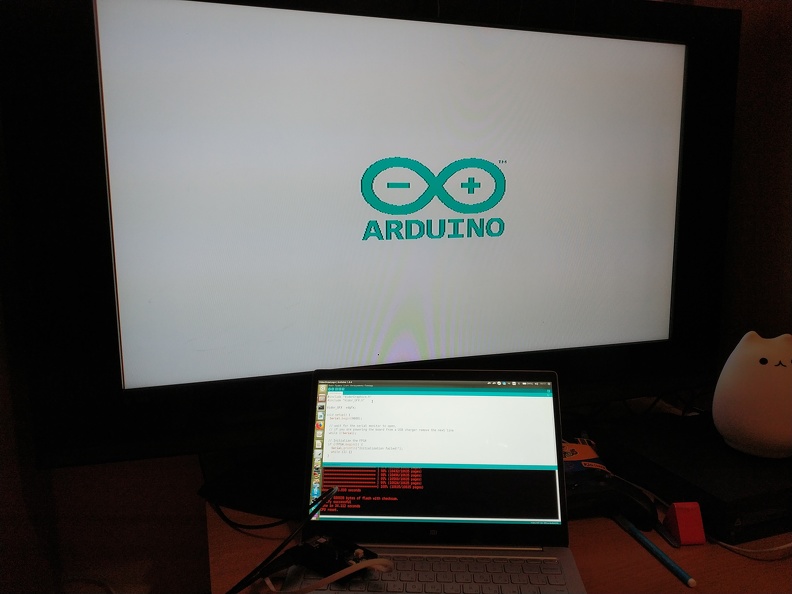

Пример, который рисует лого Ардино через HDMI на телевизоре (точнее, эта библиотека позволяет рисовать на телевизоре графические примитивы, а лого рисует уже пользовательский скетч):

https://github.com/vidor-libraries/VidorGraphics

вот внутри файл ttf (интересно, что он не двоичный, а содержит текст, внутри значения байт, разделенные запятыми):

https://github.com/vidor-libraries/VidorGraphics/blob/master/src/app.ttf

Внутри библиотеки он загружается в массив - последовательность байт:

https://github.com/vidor-libraries/VidorGraphics/blob/master/src/VidorFPGA.cpp

__attribute__ ((used, section(".fpga_bitstream")))

const unsigned char bitstream[] = {

#include "app.ttf"

};

#endif

(ога, понятно, такой текстово-двоичный формат файла ttf понимает директива include компилятора)

и где-то там, наверное, можно поискать, как он будет улетать на плату.

Исходников на Верилоге, из которых получился этот файл, судя по всему, пока нет, скорее всего их откроют вместе с недостающей частью тулчейна.

3. Далее идут примеры - пользовательские скетчи, которые обращаются к ПЛИС (точнее, к конкретной прошивке, которая туда зашита) через эту прослоечную библиотеку так же, как общаются с другими устройствами через драйвер.

https://github.com/vidor-libraries/VidorGraphics/tree/master/examples

Здесь, понятно, каждый будет лепить свое кто во что горазд. Среда - обычная ардуина, код - С++.

4. Итого тулчейн:

- Прошивка на Верилоге в обычном Квартусе файл ttf -> постпроцессор -> модифицированный ttf

- Прослоечная библиотека-драйвер, заточенная под конкретный дизайн, она же загружает на чип ttf (есть и другие сценарии прошивки вручную)

- Пользовательские скетчи - обычные скетчи Ардуино на С++

5. Предполагается, что в веб-среде будет еще какой-то графический редактор схем-дизайнов для ПЛИС для детей, но взрослые разработчики на Верилоге могут не плеваться, а просто проходить мимо сразу в Квартус.

6. Скорее всего малое количество разработчиков, знакомых с Верилогом, будут клепать прошивки ttf и оберточные библиотеки к ним. Большое количество обычных ардуинщиков, купивших плату, будут использовать их в своих скетчах, как обычные внешние устройства с драйверами. Просто увеличится количество всевозможных устройств, которые теперь не обязательно клепать в железе.

Что выйдет из затеи с графическим онлайн-редактором дизайнов для ПЛИС еще будет видно. Может быть получится что-то относительно успешное нишевое образовательное типа среды Скретч, может быть даже кто-то (у кого будет достаточно свободного времени, но он не захочет его тратить на изучение Верилог) настропалится в ней сделать что-то полезное, может быть ничего не получится. К счатью, разработчики заверяют, что раскроют тулчейн для Верилога, а значит к этому редактору ничего гвоздями прибито не будет, а значит его потенциальная сырость и вероятный провал не погребет под собой остальную платформу, которая сама по себе довольно любопытна.

7. Заводская плата приехала косячная (не шилась скетчи, завязанные на ПЛИС, проблема совсем не только у меня), но получилось исправить перепрошивкой отсюда:

http://forum.arduino.cc/index.php?topic=561393.0

(другой вариант не помог: http://forum.arduino.cc/index.php?topic=563513.0)

8. Ссылки

плата

https://store.arduino.cc/usa/arduino-vidor-4000

форум

https://forum.arduino.cc/index.php?board=125.0

библиотека-драйвер

https://github.com/vidor-libraries/VidorGraphics

шаблон проекта для Крвартус:

https://github.com/vidor-libraries/VidorFPGA

еще хороший обзор платы:

https://www.baldengineer.com/arduino-mkr-vidor-4000-hands-on.html

https://www.youtube.com/watch?v=zIlJ1a7a_k0

плюс коменты

Ruslan Tikhonov В общем, непонятно, зачем все это нужно ардуинщикам

Anton Moiseev Для обычных ардуинщиков - это потенциал для появления большего количества всевозможных "виртуальных" верилог-устройств, которые они будут загружать в плату из центрального репозитория, как обычные программные библиотеки. Ставлю на то, что первыми (после толпы всяких экспериментальных недоделанных хеллоу-волдов) появятся аппаратные ускорители каких-нибудь операций для Марлина (3д-притеры), чпу и ардупилотов. А верилогщикам одним махом на голову упала аудитория потенциальных пользователей их дизайнов - настоящих хомячков, которые будут запускать их дизайны на живых игрушках - 3д-принтерах, коптерах, всяких роботах. Честно говоря, я не в курсе, было ли и есть ли что-то похожее у экосистемы Верилога и ПЛИС до этого проекта (я не про технические решения одноплатников Контроллер+ПЛИС, которых, понятно было и есть, наверное, уже не один десяток, а про количество людей, заходящих на сайт, с которого оно продается). Насколько я понимаю, сейчас ПЛИС - это какие-то закрытые инженерные разработки и прототипы и (усилиями Юрия Панчула и ко) образовательные программы; хоббисты есть, но как разрозненные островки и зачатки. Т.е. если вы не разрабатываете профессионально и не продаете какой-то ip-блок, но что-то писать-выкладывать на Верилоге все равно хочется, то в самом лучшем случае ваш дизайн запустит какой-нибудь студент на альтеровской отладке и научится по нему проектировать процессор. Сейчас появится возможность выложить верилог-модуль в репозиторий и насобирать живых установок, хвалебных статей, обсуждений на форумах и лайков.

Roman Popov Это надо не ардуинщикам, а в первую очередь ардуино как компании. Застолбить нишу. Как сейчас со словом микроконтроллер у большинства непрофи ассоциация с ардуино, так через пару лет будет и с FPGA. Насчет упрощенной среды, то попытки уже были. Название проекта забыл (что как бы намекает), потыкал и решил что монстро-квартус с его схемотехническим редактором все же понятней.

Anton Moiseev Roman Popov весь смысл жизнеспособности ардуино заключается в том, что ее прогрммируют на обычном С++, они не стали городить свой порезанный недоязык или там оставлять один скретч, "потому, что С++ слишком сложный". Из своего они нагородили только среду и систему сборки (ну и API, но это понятно), с которыми вполне можно мириться, но при желании можно утащить значительную часть собственного кода в "большой мир". По этой причине лично я отношусь к затее с визуальным редактором схем скептически и не планирую даже его смотреть. А вот если бы они смогли раскрутить Интел на какой-нибудь консольный пакет для компиляции верилога (типа gcc) и встроили бы его в свою среду так, чтобы вероложные файлы можно было править в соседнем табе с сишниыми, это было бы достижение, но в это слабо верится, поэтому пусть будет Квартус.

Roman Popov За Интел не скажу, а вот для lattice вроде есть консольный тулкит. Кстати, латтисовская линейка чипов мне нравится больше применительно к хобби и образовательным проектам, но вот как их в наших краях приобретать - вопрос.

Визуальный редактор квартуса я использую для "сборки" проекта, т.е. отдельные модули на верилоге, но все в кучу мне удобней собрать визуально. Понятно, что рисовать там рассыпуху 74 серии (а он это позволяет) особого смысла нет.

Anton Moiseev Roman Popov это вот эти?

http://www.latticesemi.com/en/Products.aspx#_58F82ED81585418A93A8EE6349B10899

не знал про них

Roman Popov Anton Moiseev Да, эти. А вот консольный тулкит:

http://www.clifford.at/icestorm/

1. Самое интересное: прошивка для ПЛИС создается в обычном квартусе (Intel Quartus, бесплатная версия Lite), на обычном Верилоге, к среде Ардуино эта процедура никакого отношения не имеет. Из кода на верилоге Квартус генерирует файл ttf (так называемый битстрим), он дальше пойдет на ПЛИС несколькими возможными путями.

шаблон пустого проекта с топ-левел модулем, настройками и кое-какими ip-блоками (открывается, собирается, генерирует файл ttf в последнем Квартусе, проверил) здесь:

https://github.com/vidor-libraries/VidorFPGA

важный нюанс: на самом деле файл ttf, генерируемый Квартусом, как есть не подходит для прошивки чипа в плате, его предварительно нужно пропустить еще через некий постпроцессор, который производит с ним какие-то вспомогательные манипуляции. Сейчас этот инструмент не открыт, поэтому сгенерить свою прошивку из Верилога для платы вот прям сейчас не получится. Но обещают все открыть в обозримом (по словам разработчиков - в ближайшем) будущем. Можно немного подождать или попробовать сделать такой пост-процессор самостоятельно - на форуме и в статьях были кое-какие подробности, плюс можно поковырять файлы ttf, выложенные в качестве демо.

доб1: пост в фб 6 сентябня, сейчас 12 октября, вериложный тулчейн еще не открыт

доб2: когда (и если) все-таки откроют, будет повод вернуться к Верилогу

доб3: Альтера уже Интел

доб4: (из коментов) еще один производитель ПЛИС (не Xilinx и не Интел-Альтера) - Lattice: http://www.latticesemi.com/en/Products.aspx#_58F82ED81585418A93A8EE6349B10899

доб5: (из коментов) проект IceStorm - открытые утилиты для работы с ПЛИС Lattice (реверс-инжиниринг): http://www.clifford.at/icestorm/

АПДЕЙТ: 24 ноября, тулчейн открыли

https://forum.arduino.cc/index.php?PHPSESSID=a5hp71v7ioivdcl67hno0nurc2&topic=581316.0

https://github.com/vidor-libraries/VidorBitstream

2. Далее к этой прошивке ПЛИС создается обертка в виде библиотеки на С++. Она общается с ПЛИС (с конкретным дизайном, который туда зашит).

Пример, который рисует лого Ардино через HDMI на телевизоре (точнее, эта библиотека позволяет рисовать на телевизоре графические примитивы, а лого рисует уже пользовательский скетч):

https://github.com/vidor-libraries/VidorGraphics

вот внутри файл ttf (интересно, что он не двоичный, а содержит текст, внутри значения байт, разделенные запятыми):

https://github.com/vidor-libraries/VidorGraphics/blob/master/src/app.ttf

Внутри библиотеки он загружается в массив - последовательность байт:

https://github.com/vidor-libraries/VidorGraphics/blob/master/src/VidorFPGA.cpp

__attribute__ ((used, section(".fpga_bitstream")))

const unsigned char bitstream[] = {

#include "app.ttf"

};

#endif

(ога, понятно, такой текстово-двоичный формат файла ttf понимает директива include компилятора)

и где-то там, наверное, можно поискать, как он будет улетать на плату.

Исходников на Верилоге, из которых получился этот файл, судя по всему, пока нет, скорее всего их откроют вместе с недостающей частью тулчейна.

3. Далее идут примеры - пользовательские скетчи, которые обращаются к ПЛИС (точнее, к конкретной прошивке, которая туда зашита) через эту прослоечную библиотеку так же, как общаются с другими устройствами через драйвер.

https://github.com/vidor-libraries/VidorGraphics/tree/master/examples

Здесь, понятно, каждый будет лепить свое кто во что горазд. Среда - обычная ардуина, код - С++.

4. Итого тулчейн:

- Прошивка на Верилоге в обычном Квартусе файл ttf -> постпроцессор -> модифицированный ttf

- Прослоечная библиотека-драйвер, заточенная под конкретный дизайн, она же загружает на чип ttf (есть и другие сценарии прошивки вручную)

- Пользовательские скетчи - обычные скетчи Ардуино на С++

5. Предполагается, что в веб-среде будет еще какой-то графический редактор схем-дизайнов для ПЛИС для детей, но взрослые разработчики на Верилоге могут не плеваться, а просто проходить мимо сразу в Квартус.

6. Скорее всего малое количество разработчиков, знакомых с Верилогом, будут клепать прошивки ttf и оберточные библиотеки к ним. Большое количество обычных ардуинщиков, купивших плату, будут использовать их в своих скетчах, как обычные внешние устройства с драйверами. Просто увеличится количество всевозможных устройств, которые теперь не обязательно клепать в железе.

Что выйдет из затеи с графическим онлайн-редактором дизайнов для ПЛИС еще будет видно. Может быть получится что-то относительно успешное нишевое образовательное типа среды Скретч, может быть даже кто-то (у кого будет достаточно свободного времени, но он не захочет его тратить на изучение Верилог) настропалится в ней сделать что-то полезное, может быть ничего не получится. К счатью, разработчики заверяют, что раскроют тулчейн для Верилога, а значит к этому редактору ничего гвоздями прибито не будет, а значит его потенциальная сырость и вероятный провал не погребет под собой остальную платформу, которая сама по себе довольно любопытна.

7. Заводская плата приехала косячная (не шилась скетчи, завязанные на ПЛИС, проблема совсем не только у меня), но получилось исправить перепрошивкой отсюда:

http://forum.arduino.cc/index.php?topic=561393.0

(другой вариант не помог: http://forum.arduino.cc/index.php?topic=563513.0)

8. Ссылки

плата

https://store.arduino.cc/usa/arduino-vidor-4000

форум

https://forum.arduino.cc/index.php?board=125.0

библиотека-драйвер

https://github.com/vidor-libraries/VidorGraphics

шаблон проекта для Крвартус:

https://github.com/vidor-libraries/VidorFPGA

еще хороший обзор платы:

https://www.baldengineer.com/arduino-mkr-vidor-4000-hands-on.html

https://www.youtube.com/watch?v=zIlJ1a7a_k0

плюс коменты

Ruslan Tikhonov В общем, непонятно, зачем все это нужно ардуинщикам

Anton Moiseev Для обычных ардуинщиков - это потенциал для появления большего количества всевозможных "виртуальных" верилог-устройств, которые они будут загружать в плату из центрального репозитория, как обычные программные библиотеки. Ставлю на то, что первыми (после толпы всяких экспериментальных недоделанных хеллоу-волдов) появятся аппаратные ускорители каких-нибудь операций для Марлина (3д-притеры), чпу и ардупилотов. А верилогщикам одним махом на голову упала аудитория потенциальных пользователей их дизайнов - настоящих хомячков, которые будут запускать их дизайны на живых игрушках - 3д-принтерах, коптерах, всяких роботах. Честно говоря, я не в курсе, было ли и есть ли что-то похожее у экосистемы Верилога и ПЛИС до этого проекта (я не про технические решения одноплатников Контроллер+ПЛИС, которых, понятно было и есть, наверное, уже не один десяток, а про количество людей, заходящих на сайт, с которого оно продается). Насколько я понимаю, сейчас ПЛИС - это какие-то закрытые инженерные разработки и прототипы и (усилиями Юрия Панчула и ко) образовательные программы; хоббисты есть, но как разрозненные островки и зачатки. Т.е. если вы не разрабатываете профессионально и не продаете какой-то ip-блок, но что-то писать-выкладывать на Верилоге все равно хочется, то в самом лучшем случае ваш дизайн запустит какой-нибудь студент на альтеровской отладке и научится по нему проектировать процессор. Сейчас появится возможность выложить верилог-модуль в репозиторий и насобирать живых установок, хвалебных статей, обсуждений на форумах и лайков.

Roman Popov Это надо не ардуинщикам, а в первую очередь ардуино как компании. Застолбить нишу. Как сейчас со словом микроконтроллер у большинства непрофи ассоциация с ардуино, так через пару лет будет и с FPGA. Насчет упрощенной среды, то попытки уже были. Название проекта забыл (что как бы намекает), потыкал и решил что монстро-квартус с его схемотехническим редактором все же понятней.

Anton Moiseev Roman Popov весь смысл жизнеспособности ардуино заключается в том, что ее прогрммируют на обычном С++, они не стали городить свой порезанный недоязык или там оставлять один скретч, "потому, что С++ слишком сложный". Из своего они нагородили только среду и систему сборки (ну и API, но это понятно), с которыми вполне можно мириться, но при желании можно утащить значительную часть собственного кода в "большой мир". По этой причине лично я отношусь к затее с визуальным редактором схем скептически и не планирую даже его смотреть. А вот если бы они смогли раскрутить Интел на какой-нибудь консольный пакет для компиляции верилога (типа gcc) и встроили бы его в свою среду так, чтобы вероложные файлы можно было править в соседнем табе с сишниыми, это было бы достижение, но в это слабо верится, поэтому пусть будет Квартус.

Roman Popov За Интел не скажу, а вот для lattice вроде есть консольный тулкит. Кстати, латтисовская линейка чипов мне нравится больше применительно к хобби и образовательным проектам, но вот как их в наших краях приобретать - вопрос.

Визуальный редактор квартуса я использую для "сборки" проекта, т.е. отдельные модули на верилоге, но все в кучу мне удобней собрать визуально. Понятно, что рисовать там рассыпуху 74 серии (а он это позволяет) особого смысла нет.

Anton Moiseev Roman Popov это вот эти?

http://www.latticesemi.com/en/Products.aspx#_58F82ED81585418A93A8EE6349B10899

не знал про них

Roman Popov Anton Moiseev Да, эти. А вот консольный тулкит:

http://www.clifford.at/icestorm/